## PATENT SPECIFICATION

Inventors: TOM KILBURN, DAVID BEVERLEY GEORGE EDWARDS and DAVID ASPINALL.

Date of filing Complete Specification: March 14, 1961.

Application Date: March 18, 1960. No. 9720/60

Complete Specification Published: December 2, 1964.

© Crown Copyright 1964.

Index at Acceptance:—G4 A (1D, 1F, 2B, 2C, 2F2, 3A, 10G). International Classification:—G 06 f.

## COMPLETE SPECIFICATION

## DRAWINGS ATTACHED

## Improvements in or relating to Multiplying Arrangements for Digital Computing and Like Purposes

We, NATIONAL RESEARCH DEVELOPMENT CORPORATION, of 1, Tilney Street, London, W.1., a British Corporation established by Statute do hereby declare the invention, for

- 5 which we pray that a patent may be granted to us, and the method by which it is to be performed, to be particularly described in and by the following statement :--

- and by the following statement: -- This invention relates to apparatus

arrangements for effecting multiplication of numbers represented by electric signals and suitable for use in electronic binary digital computing machines.

- computing machines.

In prior Patent No. 788.927 there is

15 described a multiplier arrangement (hereinafter referred to as "of the kind described") in which a series of successive partial products for addition to one another in accumulator means are obtained by multiplying one

- 20 number, the multiplicand number, by the determined value of successive groups of digits of the other number, the multiplier number, instead of by the more usual method of forming the series of partial pro-

- 25 ducts by multiplying the first or multiplicand number by each single digit of the second or multiplier number in turn. This was effected by providing a plurality of signals each representing a different integral multiple

- 30 of the multiplicand number and then selecting the appropriate one of these multiples for presentation to the number accumulating means, each successive selection being determined by the examined value of a different

- 35 and successive group of the multiplier number digits. Thus, in a particular example, three successive binary digits of a binary multiplier number were examined as a group to determine the decimal number represented

40 thereby and then appropriate selection was

- 40 thereby and then appropriate selection was made by suitable switching means to select the appropriate one of a group of multiple versions of the binary multiplicand number

consisting of the multiplicand, twice the multiplicand, three times the multiplicand 45 and so on up to seven times the multiplicand.

976.620

The object of the present invention is to provide improved and simplified multiplier arrangements of the kind described above and in which the apparatus requirements for pro viding the different multiples of the multiplicand number are appreciably reduced and in which material saving in other ancillary apparatus requirements may be made.

In accordance with the invention, the mul- 55 tiplying arrangements include a signalcontrolled arithmetic device which can be altered in its operation from an adding function to a subtracting function, means for providing a number of signals repre- 60 senting respectively each of the different successive integral multiples of the multiplicand number from the first up to but not exceeding that multiple which is sufficient to embrace half the total number of multiples 65 capable of being signalled by the chosen number of digits forming each examined digit group in the multiplier number and means for ellecting the selection, under the control of each of such multiplier digit sig- 70 nal groups in turn, of an appropriate one of the available signals representing multiples of the multiplicand number for application to one input of said adding/subtracting device and the simultaneous control of such 75 adding/subtracting device by the same group of multiplier digits whereby it causes either addition or subtraction of the selected multiplicand multiple to or from a number 80 signal applied to the other input.

In accordance with one form of the invention, the number signal applied to the other input of the adding/subtracting device is a signal representing a chosen multiple of the multiplicand number signal which lies **85** approximately mid-way of the range of

multiples which can be signalled by the chosen number of multiplier digits forming each examined group, the particular multiple selected for application to the first input

- 5 of such adding/subtracting device and the add/subtract control being then so arranged that the output from said adding/subtracting device is a signal representing the correct partial product called for by the examined

- 10 group of multiplier digits, such partial product signal being subsequently combined in an accumulating device with any previously obtained partial product number signal so as eventually to obtain an accumulated signal

- 15 representing the required final product. In accordance with a second and preferred form of the invention, however, the said adding/subtracting device is arranged to form part of the accumulating device

- 20 itself with the signal representing the previously accumulated partial product signals applied to said other input of said adding/ subtracting device, the selection of each new multiplicand multiple and the add/subtract

- 25 control being effected in accordance with the examined values of each of the digits of each multiplier digit group and the value of the most significant digit of the previously examined multiplier digit group.

- **30** Thus, in one particular arrangement of the first form mentioned above and arranged to deal with the three binary multiplier signal digits as each examined group, the multiplicand multiples of d, 2d, 3d and 4d only

- 35 need to be made available, the convertible adding/subtracting device being arranged to be supplied with the binary multiplicand multiple 3d at its other input and with an appropriately selected one of the available40 multiples at its first input coupled with

- 40 multiples at its first input coupled with appropriate simultaneous control of the add/ subtract function of the device. Thus if the three multiplier digits signal the decimal value '4', the multiplicand in unaltered

- **45** form, i.e. *d*, is selected and the convertible adding/subtracting device is caused to add; if the decimal value of the three multiplier digits is '0', the multiplicand multiple 3*d* is selected and the convertible adding/sub-

- 50 tracting device is caused to subtract; if the decimal value of the three multiplier digits is seven, the multiplicand multiple 4d is selected and the convertible adding/sub-tracting device is caused to add and so on.

- 55 Alternatively, in a particular arrangement of the second and preferred form of the invention, again arranged to deal with three binary multiplier signal digits as each examined group, the same binary

- **60** multiplicand multiples of a. 2d, 3dand 4d are made available but the selection from these and the add/subtract control is determined not only by the examined value of each three digit multiplier group **65** but also in accordance with the examined

value '0' or '1' of the most significant digit of the three multiplier digit group which controlled the previous selection and add or subtract operation and which was of lower significance than the currently opera- 70 tive group. Thus, if the examined three multiplier digit group is found to be 100 (decimal value 4) and the most significant digit of the previous three multiplier digit group is value '0' then the selected multiplicand multiple 75 is that of 4d and the adding/subtracting circuit is caused to subtract. If however, with the same three digit group value 100, the previous most significant digit is of value '1', the selected multiplicand mul- 80 tiple is that of 3d, the adding/subtracting circuit again being caused to subtract.

In order that the nature of the invention may be more readily understood, a number of simple embodiments thereof, as applied **85** to both serial mode operation and parallel mode operation will now be described by way of illustrative example only and with reference to the drawings accompanying the provisional specification in which: **90**

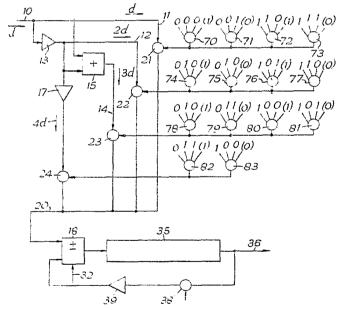

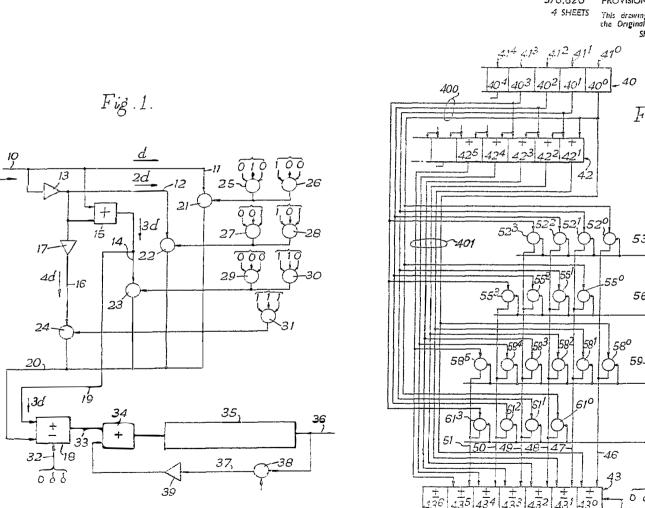

Figure 1 is a block schematic diagram of one arrangement in accordance with the invention suitable for serial mode operation with binary number signals and utilising examination of 3-digit groups of the multi- 95 plier number signal to control its operation;

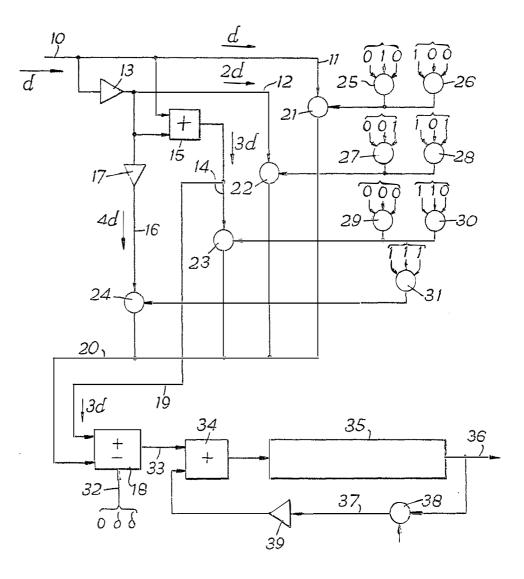

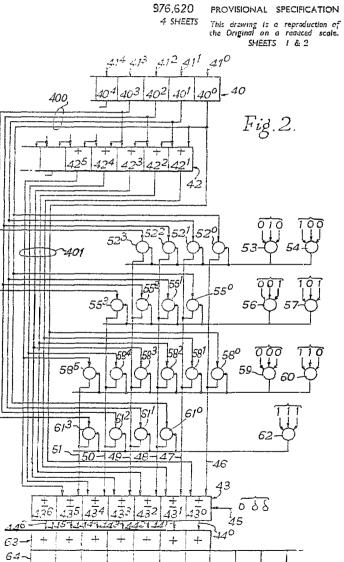

Figure 2 is a block schematic diagram of another arrangement, similar to Figure 1, but adapted for operation in the parallel mode;

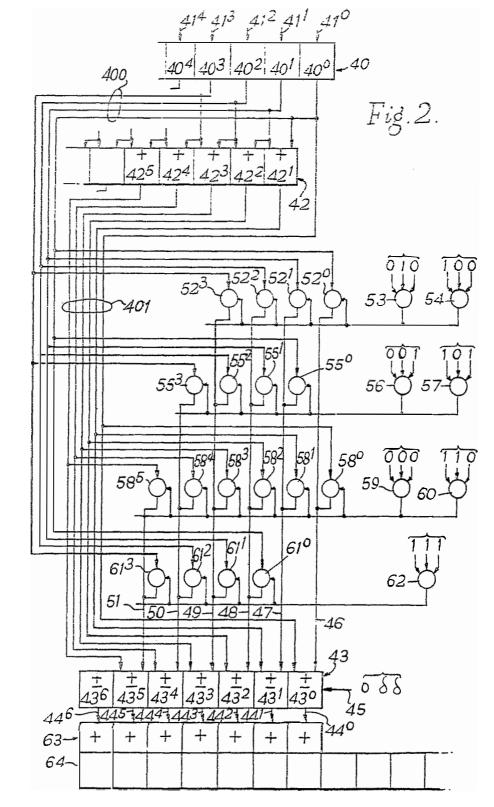

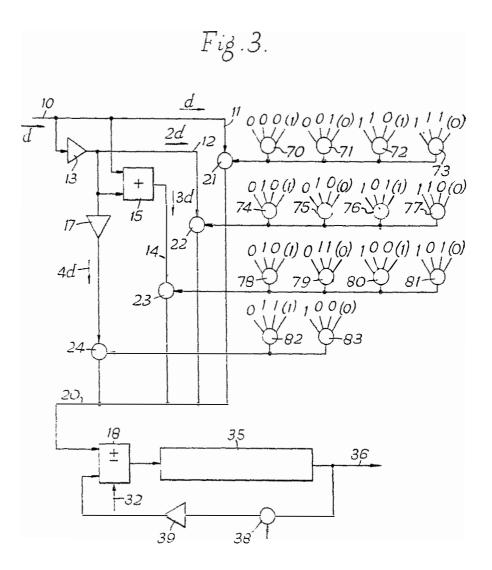

Figure 3 is a block schematic diagram of an alternative arrangement also in accordance with the invention again utilising examination of 3-digit groups of the multiplier to control its operation and adapted 105 for serial mode operation; while

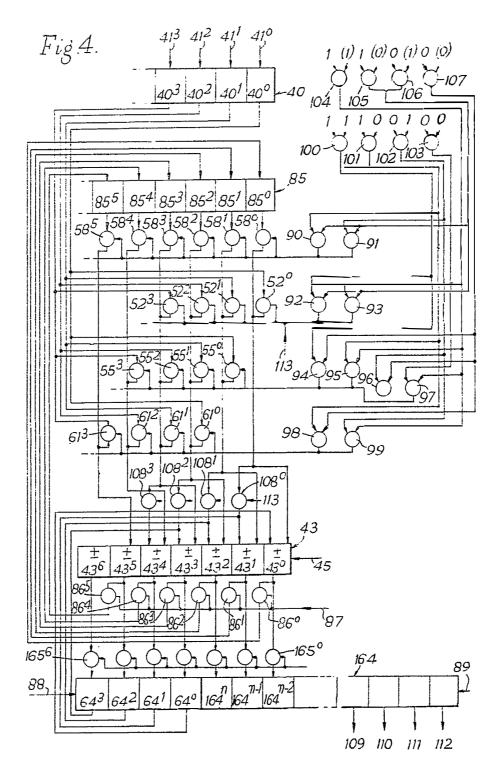

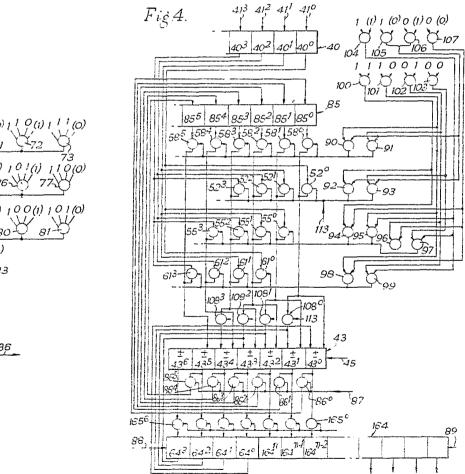

Figure 4 is a block schematic diagram of yet another arrangement, similar to Figure 3, but adapted for operation in the parallel mode. 110

Referring first to the serial mode arrangement of Fig. 1, the multiplicand number signal d in the form of an electric pulse train is assumed to be made available on input busbar 10 at each of the successive 115 operation cycles needed to form the series of partial products. This busbar 10 is connected directly by way of lead 11 to coinci-dence or AND gate 21 and by way of a delay circuit 13, which provides a delay 120 time equal to one digit interval time of the multiplicand pulse train, and lead 12 to coincidence or AND gate 22. The output signals from delay 13. which represent the multiplicand multiple 2d, are also applied 125 as one input signal to an adding circuit 15, the other input signal to which is the multiplicand signal d by way of a connection from the busbar 10. The output of this adding circuit. which represents the multiplicand 130

1**00**

multiple 3d, is applied directly by way of lead 19 to one input of an arithmetical circuit device 18 which is arranged normally to cause addition of the number

- **5** signals fed to its respective inputs but which can be altered to cause subtraction of the same input number signals by the application thereto of a suitable centrol signal on lead 32. The output signals from

- **10** the adding circuit 15 (representing the multiplicand multiple 3*d*) are also applied by way of lead 14 to the further coincidence or AND gate 23. The output signals from the delay 13 are additionally applied

- 15 by way of further delay 17, also having a delay time equal to one digit interval of the multiplicand pulse train, to provide a signal representing the multiplicand multiple 4d and this is fed over lead 16 to

- 20 coincidence or AND gate 24. The output lead of each of the gates 21, 22, 23 and 24 is connected to the second input lead 20 of the convertible adding/subtracting device 18. The output lead 33 from the

- 25 latter carries the required partial product signal representing the multiplicand number multiplied by a three-digit group of the multiplier.

- Each group of three successive multi-30 plier digits is staticised in turn by means not shown but of conventional form and conveniently resembling those shown in the aforesaid prior Patent, to provide, for each digit, separate '0' and '1' signals which

- 35 are respectively at active level when the digit is of value '0' or '1'. Such groups of staticised multiplier digit signals are applied in turn and in synchronism with an application of the multiplicand signal *d* on

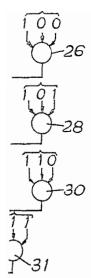

- 40 lead 10 to each of a group of further coincidence or AND gates 25, 26, 27, 28, 29, 30 and 31 in the combinations indicated by the digit values beneath the respective bracket signs, the most significant

- **45** digit being to the left in each case. Thus the gate 25 will provide an output signal for the multiplier digit group 010 (decimal value 2) whereas the gate 26 will provide an output signal for the multiplier digit

- **50** group 100 decimal value 4), while the further gates 27, 28, 29, 30 and 31 provide output signals for the respective multiplier digit groups of decimal values 1, 5,  $0_{,i}$  6 and 7.

- 55 Gates 25, 26 have their outputs connected in parallel to control gate 21: gates 27 and 28 similarly provide control outputs for gate 22: gates 29 and 30 likewise provide control outputs to gate 23 while the

- output of gate 31 controls gate 24. The control signal for the add/subtract device 18 on lead 32 is likewise derived from the group of staticised multiplier digits, being caused to subtract whenever the most

significant digit of the examined multiplier

piler digit group is of value '0' and to add whenever such most significant digit is of value '1'.

The gate circuits, such as those shown at 21, 22 . . . . 31 can be of any con-**70** venient form already well known in the art as also can be the delay circuits 13 and 17 and the adding circuit 15. The controllable add or subtract device 18 may similarly be of any suitable form now well **75** known in the art.

The manner of operation of this embodiment will be readily apparent from consideration of the following examples. If the examined multiplier digit group is 000 80 (decimal value  $\vec{0}$ ) gate 29 will be operated to provide an output which will open gate 23 thereby admitting the multiplicand multiple 3d which is available from the adding circuit 15 to the second input 20 of the **B5** adding/subtracting device 18. The same multiplicand multiple 3d is always fed directly over lead 19 to the first input of such device 18. As the most significant digit of the examined multiplier digit **90** group (000) is value '0', lead 52 will be energised to cause the add/subtract device 18 to subtract. The output on lead 33 is therefore 3d-3d or representative of the correct partial product, namely, zero. In the 95 case of an examined multiplier digit group 101 (decimal value 5), gate 28 will be operated to provide an output to open gate 22, thereby releasing the multiplicand multiple 2d available from the delay 13 to the 100 nput lead 20 to the device 18. Since the most significant digit of the examined multiplier digit group (101) is now of value '1', the control lead 32 of the add/subtract device 18 is not provided with a control 105 input and such device accordingly effects addition. The output on lead 32 is therefore 3d + 2d = 5d as is required.

The output lead 33 feeds the associated accumulator device utilised for adding to- 110 gether the various partial products as they become available one alter the other during successive operation cycles during which the different multiplier digit groups are examined in turn. This accumulator device is shown 115 as a further adding circuit 34 having one input supplied by lead 33, a shifting register or equivalent delay line 35 whose output lead 36 is connected to the second input of the adding circuit 34 by way of a regenera- 120 tion loop circuit including a control gate 38 and a delay circuit 39 whose delay time is such that, during multiplication, the output signals on lead 36 arrive back at the input to the adding circuit 34 with a three digit 125 place right shift relative to the timing of the signals of the next partial product which is to be added thereto and which is pro-vided on lead 33 as a result of the next following operation cycle using the examina- 130 tion of the next following three digit group of the multiplier number signal.

The equivalent parallel mode arrangement of Fig. 2 is shown, for simplicity. as employ-5 ing a binary multiplicand number of only four digits length but the manner of extension to deal with numbers of greater length will be self-evident.

In this embodiment, the multiplicand 10 number signal d is first registered in an appropriate multi-stage register 40 of any convenient known form, said register having successive stages such as toggle or flipflop circuits 40<sup>3</sup>, 40<sup>4</sup>, 40<sup>2</sup> and 40<sup>5</sup> controlled

- 15 respectively by input leads 41°, 41°, 41° and 41°. The group of parallel output leads 400 carry the multiplicand multiple d. A second multi-stage resister 42 serves to record the multiplicand multiple 3d, this register in-

- 25 cluding suitable adding and carry digit propagation circuits to permit its direct interconnection in the manner shown with the register 40 so that upon application of the parailel form multiplicand digit signals to

- 20 the first register over the input leads 40°, 41°.... 41°, the multiplicand multiple 3d is automatically set up on the second register stages 42°, 42°.... 42° in combination with the first stage 40° of the first

- 30 register which supplies the least significant digit of the multiple 3d also. The group of parallel output leads 401 carry the multiplicand multiple 3d.

- A convertible multi-stage parallel adding/

35 subtracting device 43 of any suitable form already well known in the art has seven stages 43<sup>3</sup>, 43<sup>1</sup> . . . . 43<sup>4</sup> and is signal-controlled over lead 45 in a manner similar to the series mode device 18 of Fig. 1, the

- **40** device 43 being arranged to operate as an adder in the absence of a control signal on lead 45 but being convertible to cause subtraction when a control signal is applied to such lead 45. Such control signal is present

- **45** only when the most significant digit of the examined three multiplier digit group is of value '0'.

A series of coincidence or AND gates  $52^{\circ}$ ,  $52^{\circ}$ ,  $52^{\circ}$ ,  $52^{\circ}$  ach controlled by the **50** parallel outputs of coincidence gates 53 and

- 50 parallel outputs of coincidence gates 53 and 54, control the connection of the four separate output leads of the group 400 from the register 40 (representing the multiplicand multiple d) to one input of each of the first

- 55 four stages 43°, 43<sup>1</sup>, 43<sup>3</sup> and 43° of the add/ subtract device 43. A further series of coincidence or AND gates 55', 55', 55° and 55°, each controlled by the parallel outputs of coincidence gates 56, 57, likewise control

- 60 the connection of the same four register output leads of the group 400 but to the four stages 43<sup>1</sup>, 43<sup>2</sup>, 43<sup>3</sup> and 43<sup>4</sup> of the add/ subtract device 43 whereby the inputs to the latter are left shifted by one place so

65 as effectively to provide the multiplicand

multiple 2d. Another similar series of coincidence gates  $61^{\circ}$ ,  $61^{\circ}$ ,  $61^{\circ}$  and  $61^{\circ}$ , each controlled by the output of coincidence gate 62, control the connection of the output leads of group 400 from the same four 70 stages of register 40 to the four stages  $43^{\circ}$ ,  $43^{\circ}$ ,  $43^{\circ}$  and  $43^{\circ}$  of the add/subtract device 43 whereby these inputs are left shifted by a further place so as effectively to provide the multiplicand multiple 4d. 75.

Another series of coincidence or AND gates  $58^3$ ,  $58^1$ , ...,  $58^5$ , each controlled by the paralleled outputs of coincidence or AND gates 59 and 60, control the connection of the group of output leads 401 **80** (representing multiplicand multiple 3*d*) from the register stages  $40^9$ ,  $42^1$ ,  $42^2$ , ...,  $42^5$ to the stages  $43^9$ ,  $43^2$ ,  $43^2$ , ...,  $43^5$  of the add/subtract device 43 while the respective leads of the same group 401 (representing **85** the multiplicand multiple 3*d*) are connected directly to the second inputs of each of the stages  $43^9$ ,  $43^7$ ,  $43^7$ , ...,  $43^6$  of the add/ subtract device 43.

The gates 53, 54, 56, 57, 59, 60 and 62 90 are analogous to the gates 25, 26 . . . . 31 of Fig. 1, being controlled by the operative group of three staticised multiplier digits. The manner of operation will be apparent from the previous description of the series- 95 mode embodiment of Fig. 1. Thus, if the currently operative group of three multiplier digits is 100 (decimal value 4) the gate 54 will be operated to provide an output which opens each of the gates 52<sup>4</sup>, 52<sup>1</sup>, 52<sup>2</sup> and 52<sup>3</sup>. 100<sup>4</sup> These connect the group of leads 400 (carrying the multiplicand multiple d) to one input of each of the stages 43, 43, 43 and 43 of the add, subtract device. The group of leads 401 (carrying the multiplicand mul- 105 tiple 3a) is connected to the second inputs of the same stages  $43^{\circ}$  . . .  $43^{\circ}$  and the further stages  $43^{\circ}$  and  $43^{\circ}$  (to allow for the greater digit length of the multiple 3d). Since the most significant digit of the multi- 110 plier digit group (100) is of value '1', the add/subtract device 43 is set to effect addition and as a result the parallel form partial product emerging on leads 44°. 44" is the correct partial product 3d + d 115 == 4d.

The parallel output leads 44°, 44<sup>1</sup>.... 44° of the adding/subtracting device 43 are connected respectively to one input of a series of further adding devices 03. The other input of such adding devices 03 is arranged to be supplied with a signal representing the current '0' or '1' state of the associated stage of the shifting register 64 while the output of each of such adding devices is 12<sup>4</sup> arranged for use as a resetting signal for the same associated stage of the register 64. In the operation of such combined shifting and adding register any applied add input over leads 44° .... 44° can be added to 130°

the already existing content of the register. The shifting register 64 forms part of the final product accumulating means. After each operation of sensing a three-digit group of

- 5 the multiplier number signal and the resultant application of a selected multiplicand multiple to the adding/subtracting device 43 along with the constantly applied multiplicand multiple 3d and following the usual

- 10 carry digit propagation in the latter, the signal state of the different stages 43<sup>3</sup>..., 43<sup>6</sup> is transferred in known manner to the interconnected stages of the adding device 63 which are already influenced by the

- 15 existing signal state of the accumulator register stages 64. These stages accordingly become altered to add in the presented new partial product. Thereafter the accumulator register 64 is caused to right shift by three

- 20 digit places prior to the next operation cycle which takes place under the control of the next three digit group of the multiplier signal.

Each of the arrangements so far described 25 requires an adding device, additional to the

- convertible adding/subtracting device employed for partial product formation, in order to add the partial product into the accumulating means. Adding devices are **30** relatively complex and expensive and a

- 30 relatively complex and expensive and a saving of the accumulator adding device together with other major economies in the case of parallel mode arrangements may be made by arranging for the selection of

35 the required multiplicand multiple and the

- 35 the required multiplicand multiple and the add/subtract control of the convertible adding/subtracting device to be dependent not only upon the examined values of the operative three-digit group of the multi-

- 40 plier but also upon the examined value of the most significant digit of the previously operative three-digit group.

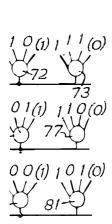

A serial mode arrangement of this second form of the invention is shown in Fig. 3

- 45 in which elements corresponding to those of Fig. 1 have been given similar reference characters. The control of the gate 21 governing the supply of the multiplicand multiple d is now by the output of any one

- 50 of four coincidence gates 70, 71, 72 and 75 controlled by the multiplier digit signals shown against each, the right hand bracketed value being that of the most significant digit of the previously operative three-digit multi-

- 55 plier group. The gate 22 governing the supply of the multiplicand multiple 2*d* is similarly controlled by the output from four further coincidence gates 74, 75, 76 and 77 each controlled by the multiplier digit signals as

- 60 shown, while gate 23 which governs the supply of the multiplicand multiple 3d is controlled by the output of four coincidence

gates 78, 79, 80 and 81 each controlled by the multiplier digit signals shown. The gate 24 which governs the supply of the multi- 65 plicand multiple 4d is controlled by the output from either of the coincidence gates 82, 83 controlled by the further multiplier digit signals shown thereagainst. The adding device 34 of Fig. 1 is eliminated, the re- 70 generation loop circuit 37 around the register 35 being now returned to the second input of the convertible adding/subtracting device 18. The latter is now controlled by the value of the most significant digit of the operative **75** three-digit multiplier group, control lead 32 being energised to cause the device 18 to subtract when such digit is of the value '1' and to add when such digit 1s of value '0'

Such an arrangement provides for multi-**80** plicand multiple selection and add/subtract control according to the following table:

| Operative   | Previous     |           |              |     |

|-------------|--------------|-----------|--------------|-----|

| multiplier  | m/s          | Addj      | Multiplicand |     |

| ligt values | di git value | Subtract  | t multipie   | 85  |

| 000         | 0            | +         | 0            |     |

| 000         | 1            | +         | d            |     |

| 001         | 0            | +         | đ            |     |

| 001         | 1            | +         | 2d           |     |

| 010         | 0            | +         | 2d           | 90  |

| 010         | 1            | +         | 3d           |     |

| $0\ 1\ 1$   | 0            | +         | 3d           |     |

| 011         | 1            | +-        | 4d           |     |

| $1 \ 0 \ 0$ | 0            | -         | 4d           |     |

| 100         | 1            |           | 3d           | 95  |

| 101         | 0            |           | 3d           |     |

| 101         | 1            |           | 2d           |     |

| $1 \ 1 \ 0$ | 0            |           | 2d           |     |

| 110         | 1            |           | d            |     |

| 111         | 0            | ife Baart | d            | 100 |

| 111         | 1            | ÷         | 0            |     |

|             |              |           |              |     |

In the operation of this embodiment, at the first examination of the three least significant digits of the multiplier number signal the value of the (non-existent) previous most 105 significant digit is assumed always to be value '0' while the number of operation cycles is increased by one to deal with the most significant digit of the multiplier number in its role of most significant 'previous' digit. 110 In this additional last operation cycle, the (non-existent) three multiplier digit group is assumed to be '000'. The arrangements of the adder/subtracter device 18 include conventional means for extending the product 115 output signal by copies of any carry over '1' digit beyond the most significant digit position of the input multiplicand signal.

The manner of operation will be made clear by the following numerical example 120 using as multiplicand (D) the binary number 001100100 (decimal value 100; and as multiplier (R) the binary number 100101001 (decimal value 297).

976,620

|    | lst cycle         | R digits $001(0) = +d =$                          | 001100100                         |

|----|-------------------|---------------------------------------------------|-----------------------------------|

|    | 2nd cycle         | right shift 3 places<br>R digits $101(0) = -3d =$ | 001100100<br>0100101100           |

|    |                   | 11                                                | 11011100000100                    |

| 5  | <b>3r</b> d cycle | right shift 3 places<br>R digits $100(1) = -3d =$ | 1111011100000100<br>0100101100    |

|    |                   | 11                                                | 11010110000000100                 |

|    | 4th cycle         | right shift 3 places<br>R digits $000(1) = +d =$  | 11110101100000000100<br>001100100 |

| 10 |                   |                                                   | 00001110100000000100              |

|    |                   |                                                   |                                   |

siving as final product the binary number: (11010000000100 (decimal 29700)

An approximately equivalent parallel mode arrangement of this second form is

15 shown in Fig. 4 where elements similar to those of Fig. 2 are also given similar reference characters. This arrangement also avoids the use of the further multi-stage adding device 42 of Fig. 2 by the provision

20 instead of a simple multi-stage register 85 having stages 85°.... 85° which are set up to register the multiplicand multiple 3d by an additional preliminary operation step in which the multiples d and 2d from the register 40 are fed to the convertible adding/ subtracting device 43 by way of gates 52°.... 52° and 108°.... 108° respectively

- each opened by energisation of the respective control leads 113. The resultant 3d out-

- **30** put signal from the device 43 is then fed back to the individual stages of the register 85 over the group of leads 402 by momentary opening of gates 86<sup>5</sup> . . . . 86<sup>5</sup> by a control signal on lead 87.

- **35** At this time the series of gates 165° .... 165° in the alternative output leads from the convertible adding/subtracting device 43 are held closed to prevent entry of this 3d multiple into the accumulator.

- 40 The group of gates  $52^{d} \dots 52^{3}$  concerned with the provision of multiple *d* are controlled by gates 92, 93 which are controlled, in turn<sub>4</sub> by the four multiplier digit values through coincidence gates 100 . . . . 103

- 45 which serve to sense the two most significant digits of the operative three-digit group and further coincidence gates 104 . . . 107 which serve to sense the least significant digit of such operative three-digit group and

- 50 the most significant digit of the previously operative three-digit group. In similar manner, the group of gates 55<sup>5</sup> . . . . 55<sup>2</sup> concerned with the provision of multiple 2d are controlled by coincidence gates 94, 95,

- 55 96 and 97 also controlled by the four multiplier digit values through gates 100 ... 107. The group of coincidence gates 58<sup>1</sup> ... 58<sup>6</sup> concerned with the provision of multiple

3d are controlled by coincidence gates 90. 91 likewise influenced by the four multi-**60** plier digit values while the group of coincidence gates  $61^{\circ}$ ...  $61^{\circ}$  concerned with the provision of multiple 4d are controlled by the four multiplier digit values through coincidence gates 98, 99. **65**

The adding/subtracting device 43 of this embodiment operates also as part of the accumulator by the connection of the outputs of the accumulator register stages  $64^{\circ}$ ....  $64^{\circ}$  by way of the lead group 403 70 to the second inputs of the stages  $43^{\circ}$ ....  $43^{\circ}$ of the convertible add/subtract device 43. The said accumulator register stages 64'.... 64<sup>3</sup> are arranged to provide output signals indicative of the '1' or '0' state thereof for **75** this purpose by application of a control or strobe pulse on lead 88. Such register stages  $64^{\circ}$  . . .  $64^{\circ}$  are also cleared to zero at the same time by this pulse. This lead 88 is activated either simultaneously with or 80 after the application of the selected multiplicand multiple to the first inputs of the said stages  $43^{\circ}$  . . .  $43^{\circ}$ . The accumulator register stages  $64^{\circ}$  . . .  $64^{\circ}$  at the most significant end of the accumulator  $164^{\circ}$  are **85** not or need not be of the shifting register type but the rmaining less significant stages  $164^n$ ,  $164^{n-1}$  . . . . of the accumulator 164 are of such shift type and operate to effect right under the control of shift signals applied 90 over control lead 89. The register stages 164<sup>n</sup>, 164<sup>n-1</sup> . . . . are right shifted by three digit places at the end of each operation step by a signal on lead 89. If desired such register. which must be of double word length, may 95 also be used initially to register the multiplier number signal in its least significant half which is always empty at the com-mencement of a multiplying operation. The four least significant digit stages of the 100 register may then correspond with the four digits used for control of multiplicand multiple selection and control of the add/subtract device 43. Outputs therefrom as shown

б

at 109 . . . 112 are then used to provide the requisite control signals to the various gates  $100 \ldots 107$  and to lead 45. Thus the outputs 109 and 110 provide signals 5 corresponding to the two most significant digits of the three operative examined digits, the respective '1' value digit signals being obtained directly from such outputs and the

- opposite '0' value digit signals being obtained 10 through inverter stages in conventional manner. Correspondingly, the outputs 111 and 112 provide signals indicating respectively the examined values of the least significant of the three operative multiplier

- 15 digits and the previous most significant digit. As with the serial mode embodiment of Fig. 3, the first operation step or cycle with the three least significant multiplier digits is made with the assumption of value

- 20 '0' for the non-existent fourth digit while after effecting the necessary number of operation cycles to deal with all of the available multiplier digits, a final step or cycle is made with an assumed zero value **25** (000) accorded to the non-existent operative

- digits of the multiplier in conjunction with the actual examined value of the most significant previous digit.

- The manner of interconnection of stages 30 43<sup>a</sup> .... 43<sup>6</sup> of the adding/subtracting device 43 to stages  $64^{\circ} \dots 64^{\circ}$  of the non-shifting part of the accumulator effectively provides an automatic three-position right shift as the related partial product digits are loaded

- 35 into the accumulator. The three-digit right shift of the remainder of the accumulator register including the stages 164<sup>n</sup>, 164<sup>n1</sup> and 164<sup>n-3</sup> is arranged to take place as the digit values of stages  $64^{\theta}$  . . .  $64^{3}$  are fed to

- 40 the adding/subtracting device 43 and such stages simultaneously cleared. All seven stages  $164^{r_2}$ ,  $164^{n_1}$ ...  $64^3$  are thus left empty in readiness for the arrival of the next partial product. The overall speed

- .45 of multiplication is accordingly improved by overlapping of the adding (or subtracting) and the shifting times while the prior shifting of the least significant part of the accumulator register also allows decoding

- 50 of the next group of multiplier digits which appear automatically in the opposite end stages of the register 164 to be overlapped with the preceding add/subtract operation.

- The multiplying apparatus elements shown 55 may also be largely employed in an associated dividing arrangement which operates to determine the quotient digits in turn singly but with right shifting of the divisor only once every three division steps

- 60 and then by three places. To effect this, advantage is taken of the facility of providing the different multiples r, 2r and 4r of the division number by means of the apparatus used for forming d, 2d and 4d during multi-65 plication. In such division, 4r is first sub-

tracted and the sign of the remainder tested. If this is positive 'l' is placed in the quotient register and 2r then selected and subtracted also. If, however, the sign is negative, '0' is placed in the quotient register and the 70 selected 2r is added. In either case the sign of the remainder is again tested and the operation repeated with r before shifting the remainder by three places.

It, will be apparent that the invention is 75 not limited to the particular arrangements as shown and described. The number of digits in each multiplier digit group may be greater or smaller than three while instead of choosing 3d as the constant input 80 to the adding/subtracting device in the first form described, another value, e.g. 4*a*, may be employed with appropriate modification of the multiplicand multiple selection and 85 adding/subtracting device control. WHAT WE CLAIM IS:

1. A multiplying arrangement of the kind described for numbers represented by electric signals which comprises a signal-controlled arithmetic device which can be 90 caused to effect either addition or subtraction of two number signals applied thereto in dependence upon a controlling signal, means for providing a number of separate signals representing 95 respectively each of the different successive integral multiples of the multiplicand number from the first multiple up to but not exceeding that multiple which is sufficient to embrace half the total number of mul- 100 tiples capable of being signalled by the chosen number of digits forming each separately examined digit group in the multiplier number and means for effecting the selection, in accordance with the 105 examined values of each of said multiplier digit signal groups in turn, of an appropriate one of said multiplicand-multiple representing signals for application as one signal input to said arithmetic device and 110 the simultaneous signal control of such device by the same group of multiplier digit signals whereby such arithmetic device causes either addition or subtraction of the selected multiplicand-multiple repre- 115 senting signal to or from a number signal applied to the other input of said arithmetic device.

2. A multiplying arrangement according to claim 1 in which said number signal 120 applied to the other input of said arithmetic device is a chosen one of said multiplicand-multiple representing signals.

3. A multiplying arrangement according to claim 1 in which said number signal 125 applied to the other input of said arithmetic device is that one of said multiplicand-multiple representing signals which represents a multiple lying substantially midway of the total range of multiples which 130

can be signalled by the chosen number of multiplier digits examined in each group and in which the selected multiplicand multiple and the add/subtract

5 control of said arithmetic device is such that the signal output from said arithmetic device represents the correct partial product called for by the examined group of multiplier digits.

10 4. A multiplying arrangement according to claim 3 which includes an accumulating device to which said partial product, representing signal is applied and by which it is combined with any previously obtained

15 partial product representing signals so as to form an eventual signal representing the final product of said multiplicand and multiplier numbers.

5. A multiplying arrangement according 20 to claim 1 in which said arithmetic device is arranged to form part of an accumulating

device including a signal register and in which the number signal applied to the other input of said arithmetic device is a signal

25 from said register representing the pre-viously accumulated partial product signals, the selection of each multiplicand-multiple representing signal for application to the first input of said arithmetic device and the

30 control of said device to add or subtract being in accordance with the examined values of each of the digits of each multiplier digit group and the value of the most significant digit of the previously

35 examined multiplier digit group.

Berwick-upon-Tweed: Printed for Her Published at The Patent Office, 25

6. A multiplying arrangement for binary number signals according to any of claims 1.5 in which each examined group of multiplier digits consists of three sequential digits and in which signals representing 40 the multiplicand multiples *a*, 2*d*, 3*a* and 4d are made available for selection.

7. A multiplying arrangement for binary number signals according to any of claims 2, 3 or 4 and 6 in which said other input 45 of said arithmetic device is supplied with the signal representing the multiplicand multiple 3ā.

8. A multiplying arrangement according to any of the preceding claims 3-7 arranges 50 for operation in the parallel mode, in which said accumulating device comprises a multistage shifting register and which includes means for sensing the digit value state of a predetermined number of the least sig- 55 nificant stages of said shifting register to provide means for examining the values of the successive multiplier digit groups by initial registration of said multiplier number signal therein. 60

9. A multiplier arrangement substantially as described and as illustrated in Fig. 1, Fig. 2, Fig. 3 or Fig. 4 of the drawings accompanying the provisional specification.

> POLLAK, MERCER & TENCH, Chartered Patent Agents, Audrey House. Ely Place, London, E.C.1. Agents for the Applicants.

Majesty's Stationery Office by The Tweeddale Press Ltd.—1964-Southampton Buildings, London, W.C.2 from which copies may be obtained.

\* ...\* ....\*

Fig . 1 .

976,620 PROVISIONAL SPECIFICATION 4 SHEETS This drawing is a reproduction of

This drawing is a reproduction of the Original on a reduced scale. SHEETS I & 2

ď

976,620 PROVISIONAL SPECIFICATION

4 SHEETS This drawing is a reproduction of the Original on a reduced scale. SHEETS 3 & 4

.

**Maria**-

976,620 PROVISIONAL SPECIFICATION 4 SHEETS This drawing is a reproduction of the Original on o reduced scale. SHEETS 3 & 4

109 110 111 112

Fig.3.