## PERFORMANCE OF A LOW POWER FULLY-DEPLETED DEEP SUBMICRON SOI TECHNOLOGY AND ITS EXTENSION TO 0.15 µm

## J. A. Burns, C. L. Keast, J. M. Knecht, R. R. Kunz, S. C. Palmateer, S. Cann, A. Soares and D. C. Shaver M.I.T. Lincoln Laboratory, Lexington, Ma. 02173

Lincoln Laboratory has developed a fully-depleted silicon-on-insulator (SOI) technology to build integrated circuits designed for very low power operation and fabricated at the limits of optical lithography. A 0.25  $\mu$ m (drawn gate length) fully-depleted SOI CMOS process technology was established using 248-nm optical lithography for initial process demonstrations, and to identify non-lithographic process integration pinch points and SOI material related issues. Design rules and SPICE parameters have been issued for the 0.25  $\mu$ m technology and a multi-project chip set assembled with circuits submitted by 15 organizations external to Lincoln Laboratory. The process technology has been adapted to Lincoln's 193-nm step-and-scan tool (1) to fabricate 0.2  $\mu$ m circuits and provide the first application of 193-nm lithography to a complete CMOS process. This paper describes the performance characteristics of the technology and the enhancements necessary to extend it to 0.15  $\mu$ m.

The 0.25  $\mu$ m fully depleted CMOS-SOI technology is designed for 0.9 volt operation and was developed by utilizing process and device design analytical techniques(2) previously developed for a 0.4  $\mu$ m bulk CMOS technology. The major features of the technology are thinning of the SOI layer by oxidation to 50 nm, island isolation by silicon etching, sidewall implantation to suppress edge leakage, an 8 nm gate oxide, dual-doped polysilicon gates, a 150 nm spacer oxide, a TiSi<sub>2</sub> salicide, and a titanium nitride, aluminum-silicon, and titanium nitride stack deposited at 500C to fill 0.4  $\mu$ m contacts. The multi-level metal process includes planarization of a plasma-deposited oxide by chemical-mechanical polishing and deposition of the second metal at 450C to fill 0.5  $\mu$ m vias. All layers were defined by plasma etch techniques. The devices reported here were fabricated on SIMOX wafers with buried oxides (BOX) of 200 and 380nm.

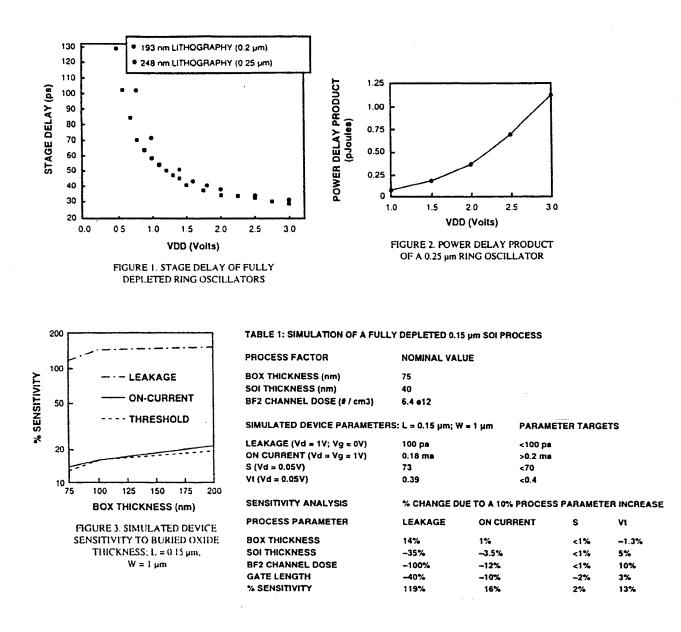

Ring oscillators and RF amplifiers were constructed with devices which had absolute thresholds less than 0.4 V, inverse subtreshold slopes less than 70 mV/decade, delta-L of 0.03 and 0.11  $\mu$ m, and normalized saturated transconductances of 0.5 and 0.2x10<sup>7</sup> cm/s for the n and p-channel devices, respectively. Ring oscillators and rf amplifiers with gate lengths of 0.25  $\mu$ m were fabricated with 248-nm lithography. The bandwidth of a 0.25  $\mu$ m amplifier was 1.62 GHz. The stage delays of 0.2 and 0.25  $\mu$ m ring oscillators are shown as functions of the the power supply voltage in Figure 1; both devices had delays less than 80 ps at Vdd=0.9 V. The 0.2  $\mu$ m circuit was fabricated using the 193-nm tool exclusively and is composed of the smallest all-optically defined transistors fabricated to date. The power delay product of the 0.25  $\mu$ m osillator with a fanout of three was 0.1 pJ at 1V as shown in Figure 2.

Extension of the technology to 0.15  $\mu$ m drawn gate lengths requires optimization of the buried oxide and SOI thickness(3). Simulation techniques were used to determine a set of process parameters to satisfy the n-channel device targets listed in Table 1 and the sensitivity of the device properties to a 10% increase in those parameters. The analysis assumed a 5 nm gate oxide and indicated that a moderately-doped drain and a boron halo implanted adjacent to the gate reduced the dependence of threshold on gate length. The results summarized in the table show that drain-source leakage is the parameter most sensitive to process variations, that it is dominated by the channel implant dose, and that it is equally affected by SOI thickness and gate length variations. The % Sensitivity listed for each device parameter in the table is the root sum of the percent change squared. It is shown in Figure 3 and indicates that a thinner BOX reduces the sensitivity of device parameters to variations in BOX and SOI thickness, channel length, and channel implant dose. Cobalt disilicide or raised source-drain structures will be required to reduce the transistor extrinsic series resistance and thereby realize the performance advantages of a 0.15  $\mu$ m design.

\* This work is sponsored by DARPA under Air Force Contract No. F19628-95-C-0002.

0-7803-3315-2

## 96CH35937

- (1) M. S. Hibbs and R. R. Kunz, SPIE Proc. 2440, 40 (1995).

- (2) Burns, J.A. et al., SRC CIM-IC Workshop, August 26, 1993

(3) Su, L. et el., IEEE Electron Device Lett., vol 15, no. 5, pp 183-185, 1994

Opinions, interpretations, conclusions, and recommendations are those of the author and are not necessarily endorsed by the United States Air Force.

## 96CH35937