# SCRIAL JAL INCLUDING TRIACS AND OTHER THYRISTORS GENERAL (%) ELECTRIC

EURELETTRONICA COMPONENTI ELETTRONICI

20145 MILANO - Via Mascheroni, 19 Tel. 49.81.851 - Telex 39102 Thomelec

# SCR MANUAL FIFTH EDITION

GENERAL ELECTRIC

Prepared by Application Engineering Centers Auburn, New York and Geneva, Switzerland

### Editors:

D. R. Grafham Mgr., Application Eng.—Geneva J. C. Hey Mgr., Application Eng.—Auburn

### Contributing Authors:

A. P. Connolly

R. W. Fox F. B. Golden

D. R. Gorss

S. R. Korn

R. E. Locher

S. J. Wu

### Layout Design: D. K. Barney

# Production:

S. Babiarz

D. Farrell

D. G. Seefeld

SEMICONDUCTOR PRODUCTS DEPARTMENT

ENERAL 6 ELECTRIC

ELECTRONICS PARK, SYRACUSE, N. Y. 13201

The circuit diagrams included in this manual are for illustration of typical semiconductor applications and are not intended as constructual information. Although reasonable care has been taken in their preparation to assure their technical correctness, no responsibility is assumed by the General Electric Company for any consequences of their use.

The semiconductor devices and arrangements disclosed herein may be covered by patents of General Electric Company or others. Neither the disclosure of any information herein nor the sale of semiconductor devices by General Electric Company conveys any license under patent claims covering combinations of semiconductor devices with other devices or elements. In the absence of an express written agreement to the contrary, General Electric Company assumes no liability for patent infringement arising out of any use of the semiconductor devices with other devices or elements by any purchaser of semiconductor devices or others.

Copyright © 1972 by the

General Electric Company, U.S.A. Electronics Park Syracuse, N.Y. 13201

### **FOREWORD**

### TO THE FIFTEENTH ANNIVERSARY EDITION OF THE SCR MANUAL

Publication of this 5th Edition marks fifteen years since General Electric introduced the first commercial SCR. Though still a teenager, the SCR has grown to be the most prominent semiconductor device for

static power conversion and control.

The fast-growing success of the SCR is paralleled by the growth of the General Electric SCR Manual, First published as an application note in 1958, the General Electric SCR Manual has been periodically revised, maintaining the basic theme of a practical, rather than theoretical, circuit and application guide for design engineers, students, teachers, and experimenters. This Edition is written by a group of engineers who, figuratively, live in the solid state power conversion arena. They are in constant touch with equipment designers and, as such, are exposed to the varied circuit problems and decisions peculiar to the application of power semiconductor devices. These authors have gained their insight and experience by contributing to literally thousands of successful design projects involving thyristors in addition to drawing on the experience and work of their predecessors.

The previous Edition has been completely reviewed in detail. Much that is new has been added, reflecting the polish that SCR applications have acquired in the past five years. These changes do not stand out as new chapters, rather, each chapter has had the additional or revised information blended in with that which remains current and valid. For those of you who have used previous editions the format remains intact to maintain any familiarity you may have developed.

The dual trends of increasing performance in military and industrial SCR's on the one hand and the shift to fabrication techniques which lend themselves to very high volume production of consumer and light industrial SCR's on the other hand are evident in the revisions to this manual. Considerably more detail is included on the parameters of SCR's along with application tips for the high performance SCR's. Information showing the designer how to approach optimum utilization of high volume, plastic encapsulated SCR's is also provided. Still, overall, considerable effort has been spent in keeping the SCR Manual concise and general in nature. For those desiring in-depth treatment of highly specialized subjects, we refer them to the comprehensive application notes listed on page 657.

I sincerely hope that you will find this new Manual useful and

informative.

H. D. Cullev

General Manager Semiconductor Products Department Syracuse, New York This 5th Edition of the SCR Manual is dedicated to one of the most competent and diverse groups of engineers ever listed on one page . . . the previous contributors to the SCR Manual, who helped lay the foundation for this fascinating technology.

A. A. Adem

J. L. Brookmire

J. H. Galloway

F. W. Gutzwiller

E. K. Howell

D. V. Jones

H. Kaufman

H. R. Lowry

N. W. Mapham

J. E. Mungenast

R. M. Muth

T. A. Penkalski

G. E. Snyder

T. P. Sylvan

E. E. Von Zastrow

### INTRODUCTION

We have not changed the SCR Manual for the sake of change. Rather we have folded into the fourth edition answers to questions which you, the equipment designers have been asking for the past few years. We have certainly included the device and circuit innovations of these past years. Finally, we have continued our past policy of presenting information in as clear, concise and uncomplicated a fashion as possible.

### HOW TO LEARN ABOUT THE SCR

If you, the reader, are already familiar with the SCR and wish guidance in the design of practical applications, this Manual is ideal for your needs. If you wish more detailed information on a specialized subject, consider the references listed at the end of each chapter, as well as the comprehensive list of General Electric application notes (p.658) which are available on request.

If you wish to explore thyristors in a more analytical sense, either as a semiconductor or as a circuit element, we refer you to "Semiconductor Controlled Rectifiers . . . Principles and Applications of p-n-p-n Devices," a book published by Prentice-Hall. Englewood Cliffs. New

Jersey.

If you have heard of the SCR but would like to start from scratch in learning how it can help you, we suggest that you obtain a copy of the General Electric "Electronics Experimenters' Circuit Manual." This manual describes some 40 ingenious circuits and projects useful in

teaching the fundamentals of electronics while constructing projects having lasting value in the automobile, home, workshop and campsite. This book was written by our application engineers on the assumption that the reader, although learned in his own field of competence, is new to the SCR and other semiconductors as well.

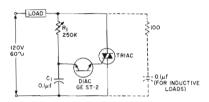

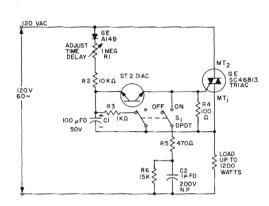

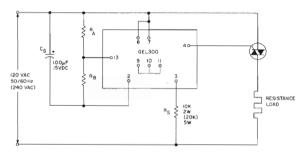

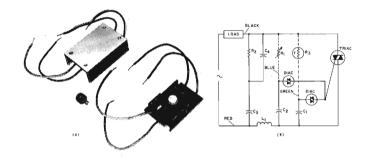

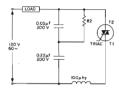

If you are really impatient to see how a basic thyristor circuit can work with your equipment load, or if you have no facilities to assemble your own circuit from electronic components, you may wish to experiment with one of several standard assemblies available from your G-E distributor. A typical standard triac variable voltage control is shown below. They are described further in Chapter 7.

### A BRIEF DESCRIPTION OF THE SCR

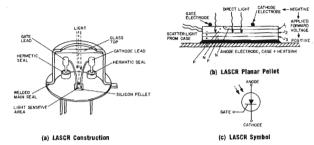

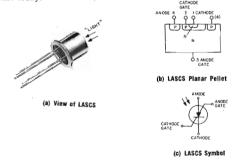

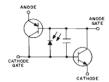

The SCR is senior and most influential member of the thyristor family of semiconductor components. Younger members of the thyristor family share the latching (regenerative) characteristics of the SCR. They include the triac, bidirectional diode switch, the silicon controlled switch (SCS), the silicon unilateral and bilateral switches (SUS, SBS), and light activated devices like the LASCR and LASCS. Most recent additions to the thyristor family are the complementary SCR, the programmable unijunction transistor (PUT) and the "assymmetrical trigger."

Let's go back to the head of the family after whom this Manual was named. The SCR is a semiconductor . . . a rectifier . . . a static latching switch . . . capable of operating in microseconds . . . and a sensitive amplifier. It isn't an overgrown transistor, since it has far greater power capabilities, both voltage and current, under both continuous and surge conditions, and can control far more watts per dollar.

As a silicon semiconductor—the SCR is compact, static, capable of being hermetically sealed, or passivated, silent in operation and free from the effects of vibration and shock. A properly designed and fabricated SCR has no inherent failure mechanism. When properly chosen and protected, it should have virtually limitless operating life even in harsh atmospheres. Thus countless billions of operations can be expected, even in explosive and corrosive environments.

As a rectifier—the SCR will conduct current in only one direction. But this serves as an advantage when the load requires DC, for here the SCR serves both to control and rectify—as in a regulated battery charger.

As a latching switch—the SCR is an ON-OFF switch, unlike the vacuum tube and transistor which are basically variable resistances (even though they too can be used as on-off switches). The SCR can be turned on by a momentary application of control current to the gate (a pulse as short as a fraction of a microsecond will do), while tubes or transistors (and the basic relay) require a continuous ON signal. In short the SCR latches into conduction, providing an inherent memory useful for many functions. The SCR can be turned ON in about one microsecond, and OFF in 10 to 20 microseconds; further improvements in switching speed are being made all along.

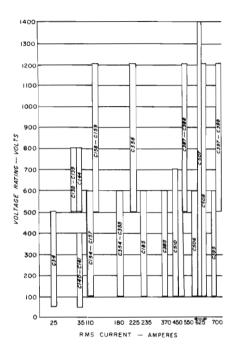

Just as a switch or relay contact is commonly rated in terms of the current it can safely carry and interrupt, as well as the voltage at which it is capable of operating, the SCR is rated in terms of peak voltage and forward current. General Electric offers a complete family of SCR's with current carrying capacities from ½ amp to 1600 amps RMS, and up to 2600 volts at this writing. Higher voltage and current loads are readily handled by series and parallel connection of SCR's.

As an amplifier—the smallest General Electric SCR's can be latched into conduction with control signals of only a few microwatts and a few microseconds duration. These SCR's are capable of switching 100's of watts. The resulting control power gain of over 10 million makes the small SCR one of the most sensitive control devices available. With a low cost unijunction transistor firing circuit driving the larger SCR's, stable turn-on control power gains of many billions are completely practical. This extraordinary control gain makes possible inexpensive control circuits using very low level signals, such as produced by thermistors, cadmium sulfide light sensitive resistors, and other transducers.

Most of the foregoing list of assets of the SCR apply equally well to the other members of the thyristor family as you will see in this Manual. Meanwhile the shortcomings and limitations of thyristors become less significant as the years pass. Newly introduced high voltage and bidirectional types lift the transient and operating voltage barriers. High speed thyristors allow operation at ultrasonic frequencies and under severe dynamic conditions, and lower semiconductor costs permit use of higher current rated thyristors instead of critically designed and expensive overcurrent protection systems.

Best of all, SCR's and thyristors for every type of application . . . industrial, military, aerospace, commercial, consumer . . . are more economical than ever. Best indication of this is the rapidly increasing tempo of applications of the new plastic-encapsulated thyristors in high volume consumer applications where every penny is critical.

Here are just some of the conventional types of controls and elements that thyristors are busy replacing and improving upon:

Thyratrons Relavs Magnetic Amplifiers Ignitrons M-G Sets Rheostats Power Transistors Motor Starters Transformers Limit Switches Constant Voltage Transformers Saturable Reactors Contactors Variable Autotransformers Fuses Timers Vacuum Tubes Thermostats Mechanical Speed Changers Centrifugal Switches Ignition Points

Welcome to the exciting world of the thyristor family, its circuits and applications. Please bear in mind that the material in this Manual is intended only as a general guide to circuit approaches. It is not allencompassing. However, our years of experience in offering application help have shown that, given some basic starting points like those in this Manual, you the circuit designer inevitably come up with the best, and often unique, approach for your particular problems.

We, in particular, would like to direct your attention to Chapter 20, "Selecting the Proper Thyristor and Checking the Completed Circuit Design." Here, we have tried to pull together a roadmap of the route to successful design with thyristors avoiding the pitfalls we, and others, have learned the hard way.

You will find the "Application Index" on pages 671 a useful guide in starting the search for the ideal circuit for your application. The list of Application Notes starting on page 674 will also provide specialized help beyond the detail of this Manual.

## TABLE OF CONTENTS

| 1. CONSTRUC | TION AND BASIC THEORY OF OPERATION                                      |

|-------------|-------------------------------------------------------------------------|

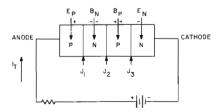

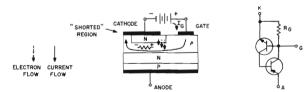

| 1.1         | What is a Thyristor?                                                    |

| 1.2         | Classification of Thyristors                                            |

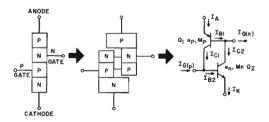

| 1.3         | Two Transistor Analogy of PNPN Operation                                |

| 1.4         | Reverse Blocking Thyristor (SCR) Turn-Off Mechanism                     |

| 1.5         | Improvements for Dynamic SCR Operation                                  |

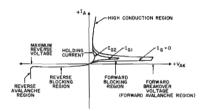

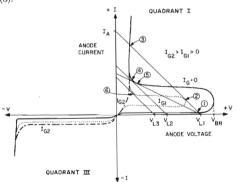

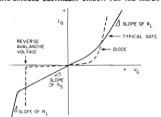

| 1.6         | V-I Characteristics of Reverse Blocking Triode or<br>Tetrode Thyristors |

| 1.7         | Gate Turn-Off Switch or Gate Controlled Switch 1                        |

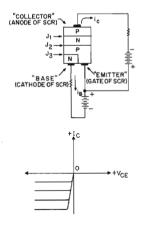

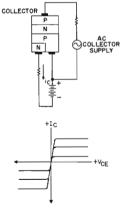

| 1.8         | Thyristor Used as a Remote Base Transistor                              |

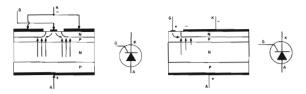

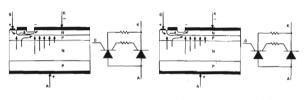

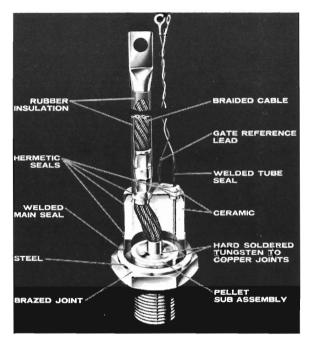

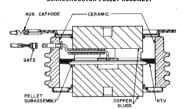

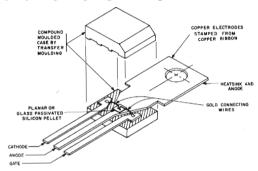

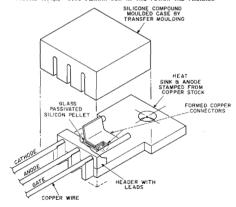

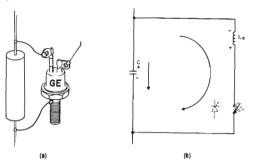

| 1.9         | Thyristor Construction                                                  |

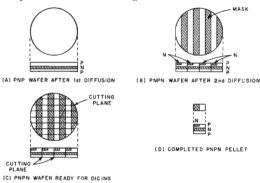

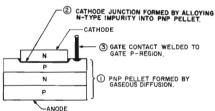

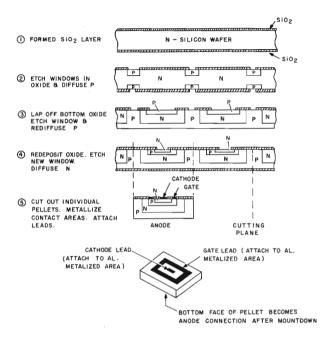

| 1.9.1       | Pellet Fabrication                                                      |

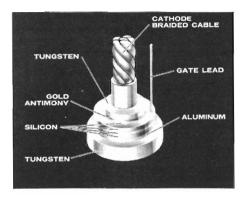

| 1.9.2       | Pellet Encapsulation                                                    |

| 1.10        | Comparison of Thyristors With Other Power                               |

|             | Semiconductors 2                                                        |

|             | AND TERMINOLOGY                                                         |

|             | AND TERMINOLOGY                                                         |

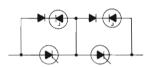

| 2.1         | Semiconductor Graphical Symbols 2                                       |

| 2.2         | SCR Terminology 2                                                       |

| 2.2.1       | Subscripts 2                                                            |

| 2.2.2       | Characteristics and Ratings                                             |

| 2.2.3       | Letter Symbol Table                                                     |

| 2.2.4       | General Letter Symbols                                                  |

| 3. RATINGS  | AND CHARACTERISTICS OF THYRISTORS                                       |

| 3.1         | Junction Temperature                                                    |

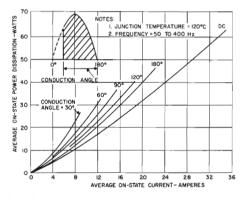

| 3.2         | Power Dissipation                                                       |

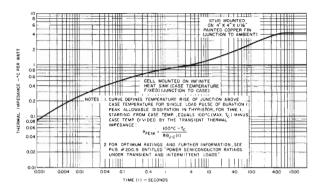

| 3.3         | Thermal Resistance                                                      |

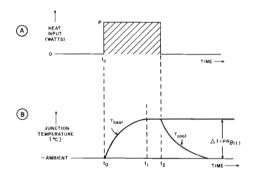

| 3.4         | Transient Thermal Impedance                                             |

| 3.4.1       | Introduction                                                            |

| 3.4.2       | The Transient Thermal Impedance Curve 3                                 |

| 3.4.3       | The Effect of Heatsink Design on the Transient                          |

|             | Resistance Curve 4                                                      |

| 3.5         | Recurrent and Non-Recurrent Current Ratings 4                           |

| 3.5.1       | Introduction 4                                                          |

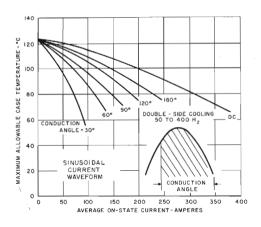

| 3.5.2       | Average Current Rating (Recurrent) 4                                    |

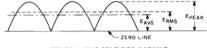

| 3.5.3       | RMS Current (Recurrent) 4                                               |

| 3.5.4       | Arbitrary Current Waveshapes and Overloads (Recurrent)                  |

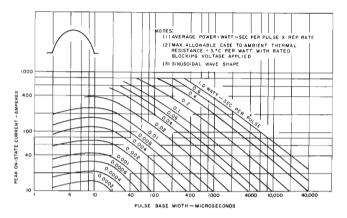

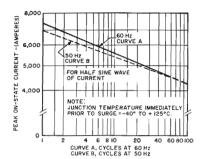

| 3.5.5       | Surge and I <sup>2</sup> t Ratings (Non-Recurrent) 4                    |

| 3.6         | Basic Load Current Rating Equations 4                                   |

| 3.6.1       | Introduction 4                                                          |

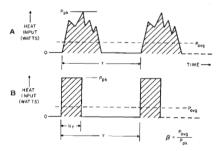

| 3.6.2       | Treatment of Irregularly Shaped Power Pulses -                          |

|             | Approximate Method 4                                                    |

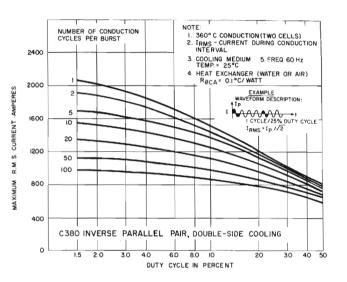

| 3.6.3       | Resistance Welding Ratings for Recurrent                                |

|             | Pulse Bursts                                                            |

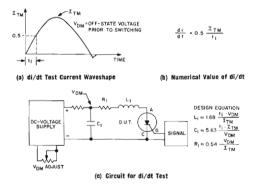

| 3.7         | Recurrent and Non-Recurrent di/dt Ratings 5                             |

| 3.7.1       | Introduction 5                                                          |

| 3.7.2       | Industry Standard di/dt Rating (Recurrent) 5                            |

### SCR MANUAL

| 3.7.3                                                                                                                                                                        | Concurrent di/dt Rating (Recurrent)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 54                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 3.7.4                                                                                                                                                                        | Industry Standard di/dt Rating (Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |

|                                                                                                                                                                              | Triggered — Non-Recurrent)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                                                                |

| 3.7.5                                                                                                                                                                        | Industry Standard di/dt Rating (V(BO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                   |

|                                                                                                                                                                              | Triggered — Non-Recurrent)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                                                                |

| 3.7.6                                                                                                                                                                        | Turn-On Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55                                                                                                                |

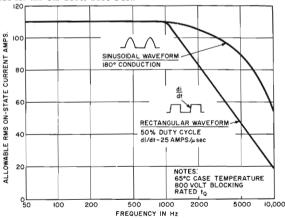

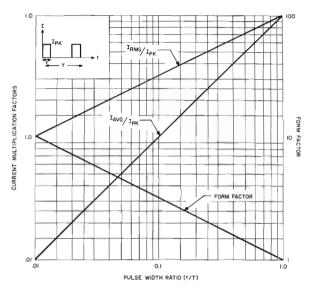

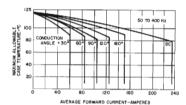

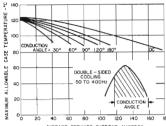

| 3.8                                                                                                                                                                          | High Frequency Current Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56                                                                                                                |

| 3.8.1                                                                                                                                                                        | High Frequency Sinusoidal Waveshape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                   |

|                                                                                                                                                                              | Current Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56                                                                                                                |

| 3.8.2                                                                                                                                                                        | High Frequency Rectangular Waveshape                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                   |

|                                                                                                                                                                              | Current Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58                                                                                                                |

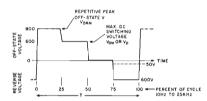

| 3.9                                                                                                                                                                          | Voltage Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                                                                |

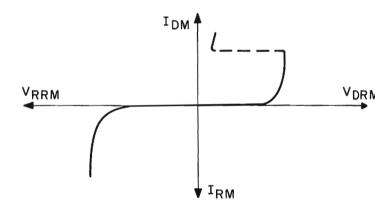

| 3.9.1                                                                                                                                                                        | Reverse Voltage (V <sub>RRM</sub> ) and (V <sub>RSM</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                                                                                |

| 3.9.2                                                                                                                                                                        | Peak Off-State Blocking Voltage (VDRM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                                                                |

| 3.9.3                                                                                                                                                                        | Peak Positive Anode Voltage (PFV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                                                                                                |

| 3.9.4                                                                                                                                                                        | Voltage Ratings for High Frequency,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                   |

|                                                                                                                                                                              | Blocking Power Limited SCR's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 62                                                                                                                |

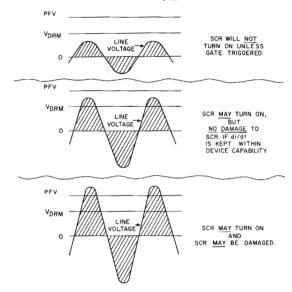

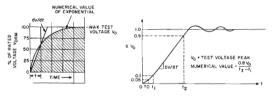

| 3.10                                                                                                                                                                         | Rate of Rise of Off-State Voltage (dv/dt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63                                                                                                                |

| 3.10.1                                                                                                                                                                       | Static dv/dt Capability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64                                                                                                                |

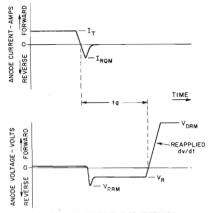

| 3.10.2                                                                                                                                                                       | Reapplied dv/dt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                                                                                |

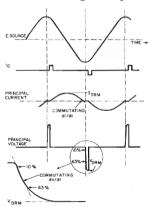

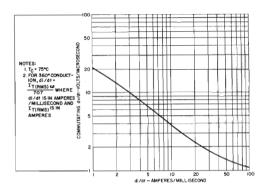

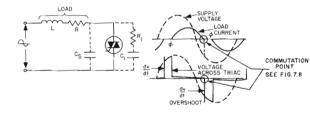

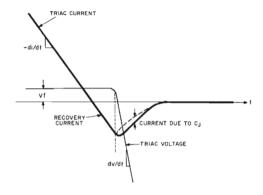

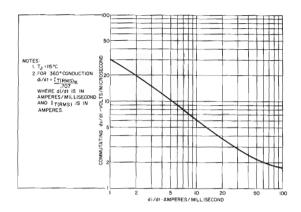

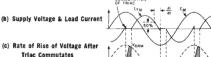

| 3.10.3                                                                                                                                                                       | Triac Commutating dv/dt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                                                                |

| 3.11                                                                                                                                                                         | Gate Circuit Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67                                                                                                                |

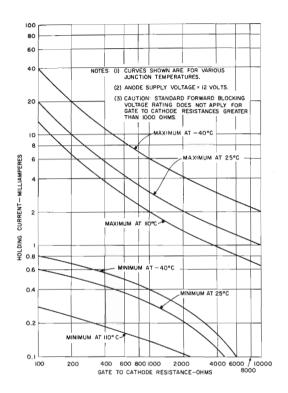

| 3.12                                                                                                                                                                         | Holding and Latching Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 67                                                                                                                |

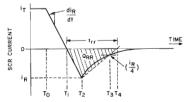

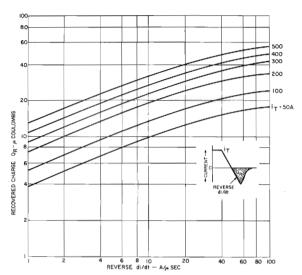

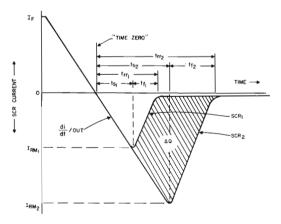

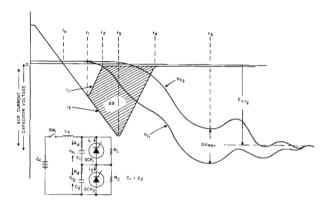

| 3.13                                                                                                                                                                         | Reverse Recovery Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                                                                                                |

| 3.13                                                                                                                                                                         | novoice receivery characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00                                                                                                                |

|                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                   |

|                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                   |

| 4 0475 754                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                   |

|                                                                                                                                                                              | GGER CHARACTERISTICS, RATINGS AND METHODS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71                                                                                                                |

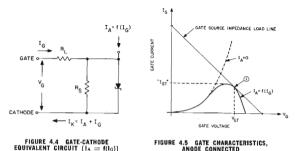

| 4.1                                                                                                                                                                          | The Triggering Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71                                                                                                                |

| 4.1<br>4.2                                                                                                                                                                   | The Triggering Process SCR Gate-Cathode Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71<br>73                                                                                                          |

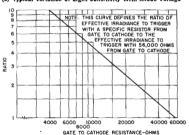

| 4.1<br>4.2<br>4.2.1                                                                                                                                                          | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71<br>73<br>73                                                                                                    |

| 4.1<br>4.2<br>4.2.1<br>4.2.2                                                                                                                                                 | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71<br>73<br>73<br>74                                                                                              |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3                                                                                                                                        | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71<br>73<br>73<br>74<br>74                                                                                        |

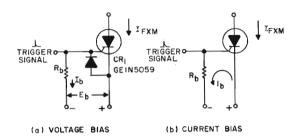

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3                                                                                                                                 | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 71<br>73<br>73<br>74<br>74<br>76                                                                                  |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1                                                                                                                        | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71<br>73<br>73<br>74<br>74<br>76<br>76                                                                            |

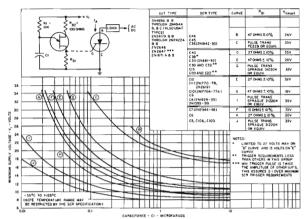

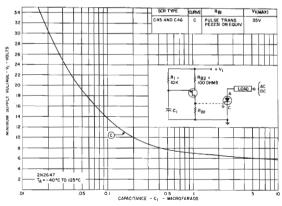

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2                                                                                                               | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Cate-Cathode Resistance Gate-Cathode Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77                                                                      |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1                                                                                                                        | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71<br>73<br>73<br>74<br>74<br>76<br>76                                                                            |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2                                                                                                               | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Cate-Cathode Resistance Gate-Cathode Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77                                                                      |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                                                                                    | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode Inductance                                                                                                                                                                                                                                                                                                                                                                                                               | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77<br>78<br>79                                                          |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                                             | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode Inductance Gate-Cathode LC Resonant Circuit Positive Gate Bias                                                                                                                                                                                                                                                                                                                                                           | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77<br>78<br>79                                                          |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5                                                                                    | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering. Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode Inductance Gate-Cathode LC Resonant Circuit                                                                                                                                                                                                                                                                                                                                                                             | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77<br>78<br>79                                                          |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6                                                                           | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode Inductance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit                                                                                                                                                                                                                                                                                             | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77<br>78<br>79<br>79                                                    |

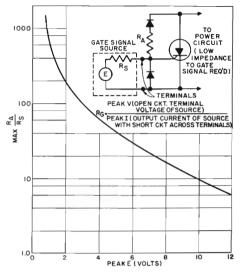

| 4.1<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4                                                                           | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode Inductance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications                                                                                                                                                                                                                                                           | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77<br>78<br>79<br>79<br>81<br>84                                        |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4                                                                    | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode Inductance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines                                                                                                                                                                                                                                                | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77<br>78<br>79<br>79<br>81<br>84<br>85<br>85                            |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.6                                                      | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Cate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR                                                                                                                                                                                                                        | 711<br>733<br>744<br>766<br>777<br>788<br>79<br>79<br>81<br>844<br>85<br>85<br>87                                 |

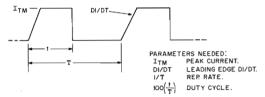

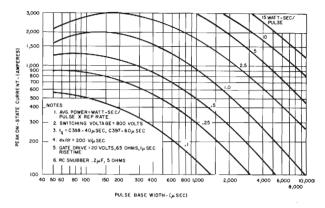

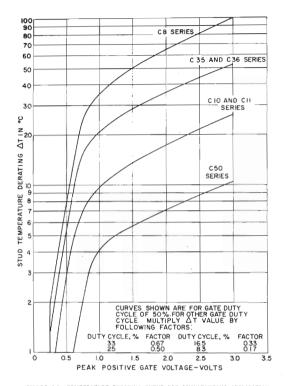

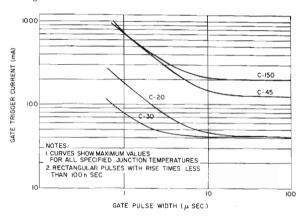

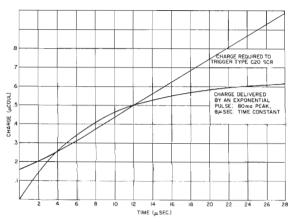

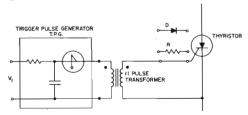

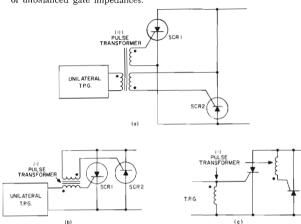

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.6<br>4.7                                               | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR Pulse Triggering                                                                                                                                                                                                       | 71<br>73<br>73<br>74<br>74<br>76<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>85                                  |

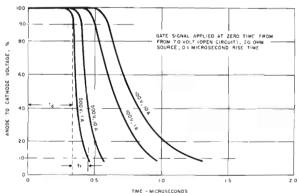

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9                                 | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode Inductance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR Pulse Triggering Anode Turn-On Interval Characteristics                                                                                                                                        | 711<br>733<br>744<br>746<br>766<br>777<br>788<br>79<br>79<br>811<br>844<br>855<br>87<br>87<br>90                  |

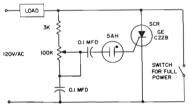

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10                         | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR Pulse Triggering Anode Turn-On Interval Characteristics Simple Resistor and RC Trigger Circuits                                                                                                                        | 71<br>73<br>73<br>74<br>76<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>87<br>87<br>90<br>91                      |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11                        | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Cate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR Pulse Triggering Anode Turn-On Interval Characteristics Simple Resistor and RC Trigger Circuits Triggering SCR With a Negative Pulse                                                                                   | 71<br>73<br>73<br>74<br>76<br>76<br>77<br>78<br>79<br>81<br>84<br>85<br>85<br>87<br>90<br>91<br>94                |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12         | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR Pulse Triggering Anode Turn-On Interval Characteristics Simple Resistor and RC Trigger Circuits Triggering SCR With a Negative Pulse AC Thyratron-Type Phase Shift Trigger Circuits                                    | 711<br>733<br>744<br>766<br>777<br>78<br>79<br>81<br>84<br>85<br>85<br>87<br>90<br>91<br>94<br>95                 |

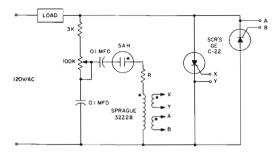

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12<br>4.13 | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR Pulse Triggering Anode Turn-On Interval Characteristics Simple Resistor and RC Trigger Circuits Triggering SCR With a Negative Pulse AC Thyratron-Type Phase Shift Trigger Circuits Saturable Reactor Trigger Circuits | 711<br>733<br>744<br>746<br>766<br>777<br>788<br>799<br>811<br>844<br>855<br>879<br>90<br>911<br>944<br>955<br>95 |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.3<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>4.3.5<br>4.3.6<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9<br>4.10<br>4.11<br>4.12         | The Triggering Process SCR Gate-Cathode Characteristics Characteristics Prior to Triggering Characteristics at Triggering Point Characteristics After Triggering Effects of Gate-Cathode Impedance and Bias Gate-Cathode Resistance Gate-Cathode Capacitance Gate-Cathode LC Resonant Circuit Positive Gate Bias Negative Gate Bias Effects of Anode Circuit Upon Gate Circuit DC Gate Triggering Specifications Load Lines Positive Gate Voltage That Will Not Trigger SCR Pulse Triggering Anode Turn-On Interval Characteristics Simple Resistor and RC Trigger Circuits Triggering SCR With a Negative Pulse AC Thyratron-Type Phase Shift Trigger Circuits                                    | 711<br>733<br>744<br>764<br>766<br>777<br>788<br>79<br>79<br>811<br>844<br>855<br>87<br>90<br>91<br>94<br>95      |

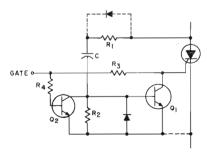

| 4.14                                                             | Semiconductor Trigger-Pulse Generators                                                                                                                                                                                                                                                                                                                                                                                    | 98                                                          |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

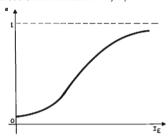

| 4.14.1                                                           | Basic Relaxation Oscillation Criteria                                                                                                                                                                                                                                                                                                                                                                                     | 98                                                          |

| 4.14.2                                                           | Unijunction Transistor                                                                                                                                                                                                                                                                                                                                                                                                    | 100                                                         |

| 4.14.2.1                                                         | Basic UJT Pulse Trigger Circuit                                                                                                                                                                                                                                                                                                                                                                                           | 102                                                         |

| 4.14.2.2                                                         | Designing the Unijunction Transistor                                                                                                                                                                                                                                                                                                                                                                                      |                                                             |

|                                                                  | Trigger Circuit                                                                                                                                                                                                                                                                                                                                                                                                           | 103                                                         |

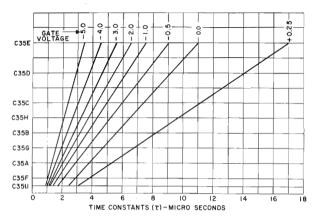

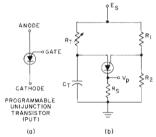

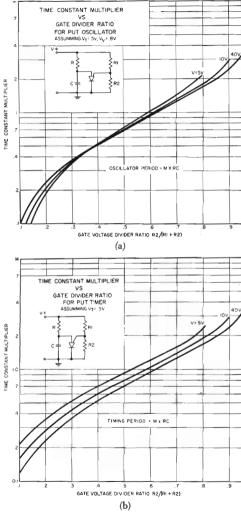

| 4.14.3                                                           | Programmable Unijunction Transistor (PUT)                                                                                                                                                                                                                                                                                                                                                                                 | 105                                                         |

| 4.14.3.1                                                         | Designing the PUT Relaxation Oscillator                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

|                                                                  | and Timer Circuits                                                                                                                                                                                                                                                                                                                                                                                                        | 106                                                         |

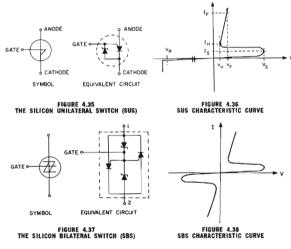

| 4.14.4                                                           | Silicon Unilateral Switch (SUS)                                                                                                                                                                                                                                                                                                                                                                                           | 109                                                         |

| 4.14.5                                                           | Silicon Bilateral Switch (SBS)                                                                                                                                                                                                                                                                                                                                                                                            | 110                                                         |

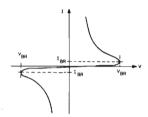

| 4.14.6                                                           | Bilteral Trigger Diode (Diac)                                                                                                                                                                                                                                                                                                                                                                                             | 110                                                         |

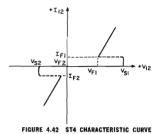

| 4.14.7                                                           | Asymmetrical AC Trigger Switch (ST4)                                                                                                                                                                                                                                                                                                                                                                                      | 111                                                         |

| 4.14.8                                                           | Other Trigger Devices                                                                                                                                                                                                                                                                                                                                                                                                     | 112                                                         |

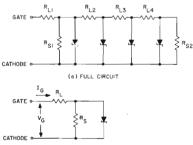

| 4.14.9                                                           | Summary of Semiconductor Trigger Devices                                                                                                                                                                                                                                                                                                                                                                                  | 112                                                         |

| 4.15                                                             | Neon Glow Lamps as Trigger Devices                                                                                                                                                                                                                                                                                                                                                                                        | 113                                                         |