| Technical Report: | RF     | 06/97 |

|-------------------|--------|-------|

| Date :            | 5 May, | 1997  |

Title :

# NTB39 MULTICHIP DESCRIPTION (STA001 DEVELOPMENT)

Distribution:

P. Erratico R. Ferrari V. Saviotti M.Paparo C. Paul (FhG) T. Von Der Grun (FhG) F. Dantoni M. Melito S. Dossi

# RF Design Group

Technical Supervisor: *P.Vita*

Author:

Giovanni Cali'

#### INTRODUCTION

The STA001 is an RF IC using SGS-Thomson Microelectronics HSB2 High Speed Bipolar Technology for one chip solution for the Starman digital satellite radio receiver. The chip includes all the RF functions up to IF and manages the signals to and from the baseband.

MAIN DESCRIPTION

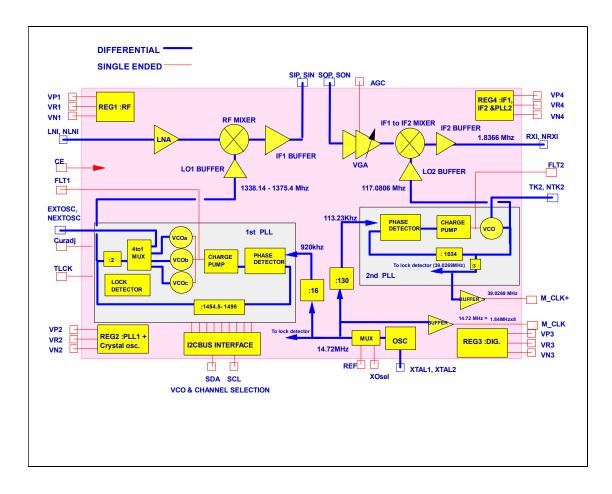

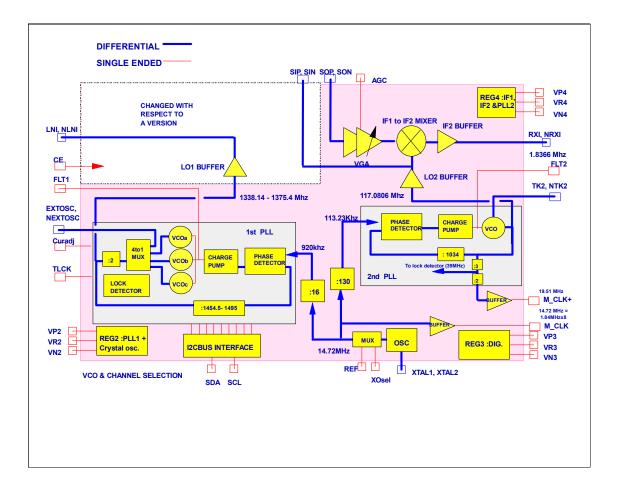

The device implement a superetherodyne completely integrated RF frontend for a QPSK receiver. The system is a receiving chain that transforms the RF incoming signal in a "low IF" signal performing two different frequency conversions from the 1452 ~ 1492 MHz band to a signal centered at a carrier of 1.84MHz. Every channel has a 2.5 MHz bandwidth.

To perform theese operations the system needs several gain blocks and the synthesizing of two different LO frequency, one programmable (the LO1 signal, it is needed to get the desired channel in the SAW filter bandwidth) and one fixed (the LO2 signal, it is needed to shift the carrier to the first IF to the second "low IF". The gain of the receiving chain is able to generate starting from the RF signal a 1Vpp signal output needed from the A/D converters.

For any further detailed circuit description and feature please refer to the STA001 data sheet.

#### **STA001 MULTICHIP DESCRIPTION**

The STA001 specification has some critical issues related with two main points:

The LO1 signal generation (1.4GHz about) is quite critical because it is quite difficult to reach with an external tank circuit; parasitics from bonding, package and application board could be very difficult to manage. Solution with completely integrated tank is choosen as preferred solution.

STA001 is an RF frontend working with two PLLs running together on sylicon: rejection from noisy supplies could be determinant in the overall performance of the circuit. Solution with a differential input LNA (balun outside) is to be considered as preferred solution.

The different versions are described below.

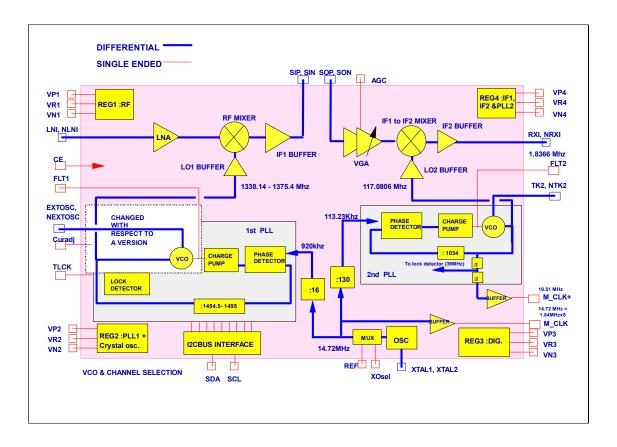

#### STA001 A

# The A version is the baseline chip. It implements a differential LNA and a completely integrated tank multi-VCOs RF structure.

The aim of the three VCOs is to cover the spread of the internal devices, parasitics and temperature drift. The VCOs are exclusively selected during the setup procedure described in the data

sheet; they are running at double frequency of LO1 for phase noise, sylicon area and leakage from LO to signal limiting reasons (see block diagram).

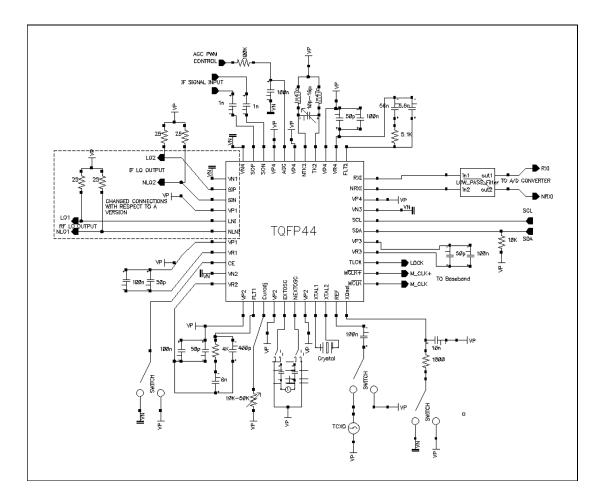

The connections needed for testing and application are showed below.

#### STA001 B

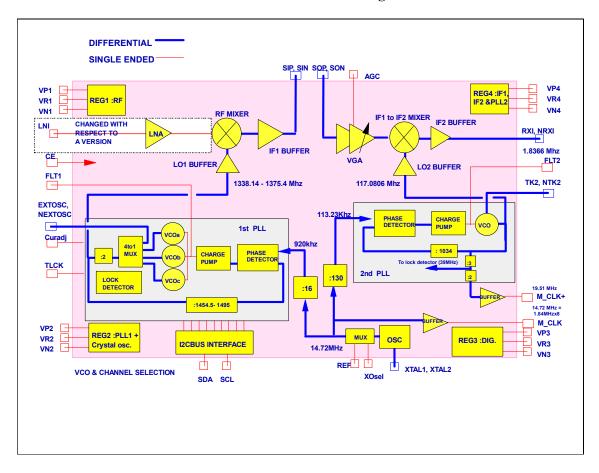

<u>The B version implements a differential LNA and a completely external tank (vari-</u> <u>caps+inductors) RF VCO solution. All the others internal blocks are identical to version A.</u> Please refer to the structure showed in block diagram B. The connections needed for testing and application are showed below.

# STA001 BB

The BB version implements a differential LNA and partially external tank (integrated varicaps, external inductors) RF VCO solution. All the others internal blocks are identical to version A. Please refer to the structure showed in block diagram B (only RF tank changes with respect to version B).

The connections needed for testing and application are showed below.

#### STA001 C

<u>The C version implements a single-ended input LNA and a completely integrated tank multi-</u> <u>VCOs RF structure. All the others internal blocks are identical to version A.</u>

If its behaviour with "noisy supply" will be good, C version could be the best one because it's the cheapest solution (no balun needed). Also the intrinsic behavior without matching network (minimum return loss needed 10dB) should be better than differential solution. Please refer to the block diagram C.

The connections needed for testing and application are showed below.

#### STA001 D

The D version is completely equal to version A but with a "3 wires interface" replacing the I2CBUS interface. All the others internal blocks are identical to version A.

Please refer to the structure showed in block diagram D. The connections needed for testing and application are showed below.

#### STA001 E

The E version is completely equal to version A but without RF LNA, Mixer and SAW buffer and with the oscillator signals LO1, LO2 available on pins. All the others internal blocks are identical to version A.

The LO1 and LO2 signal are available in differential open collector mode. By connecting outputs to VP by two 25 Ohms resistors (50 Ohms differential output impedance) the LO oscillators power will be -16dBm about.

The aim of this version is to build up a multi-chip working structure in case of bad-working RF signal blocks.

Please refer to the structure showed in block diagram E. The connections needed for testing and application are showed below.

#### STA001 F

<u>The F version is completely equal to version A but it implements different circuital solutions</u> for 2nd mixer and output buffer. All the others internal blocks are identical to version A.

For block scheme, pin out, application and testing it has to be considered identical to version

A.

The connections needed for testing and application are showed below.

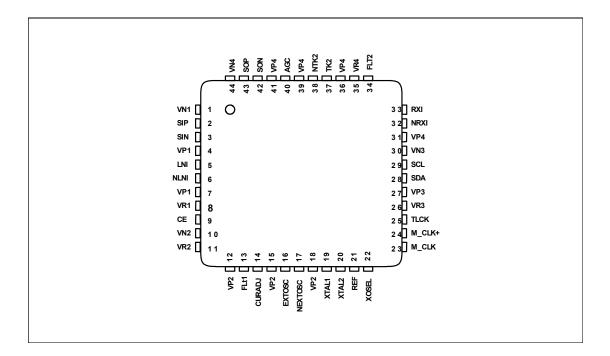

#### **PINS CONNECTION**

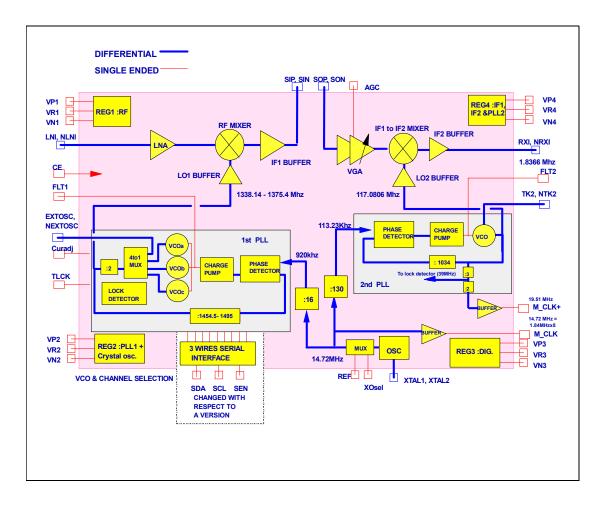

#### STA001 version A Block diagram

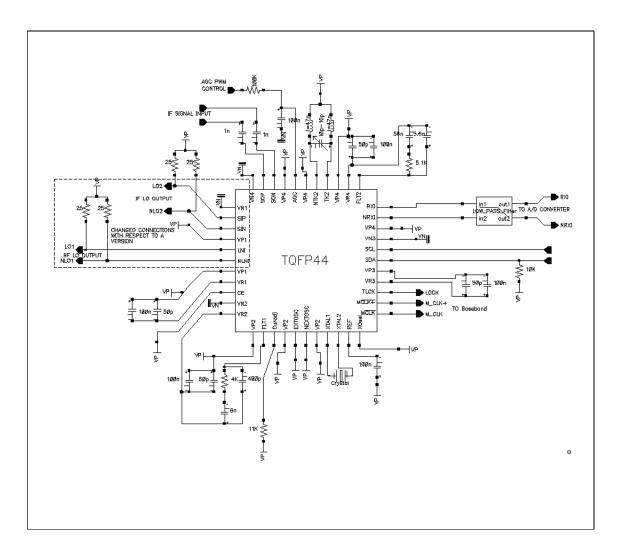

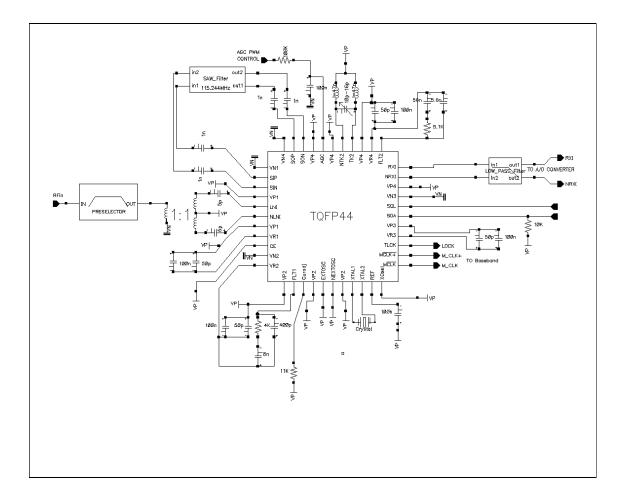

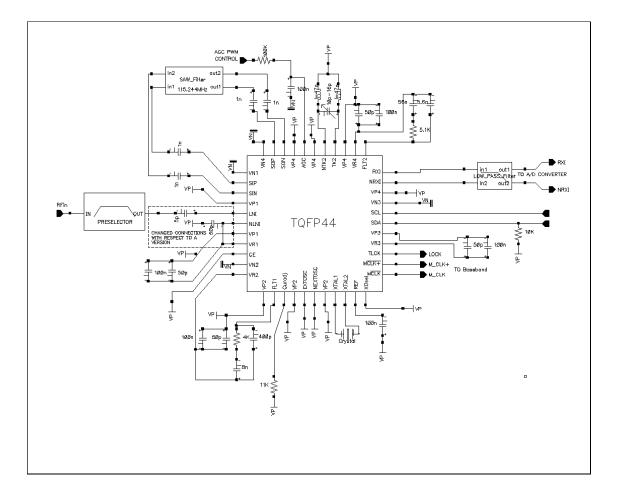

# STA001 version A Testing board

# **STA001 version A Application board**

#### STA001 version B & BB Block diagram

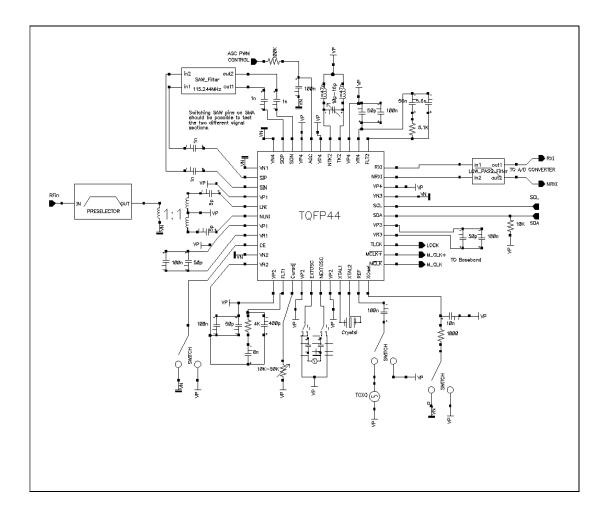

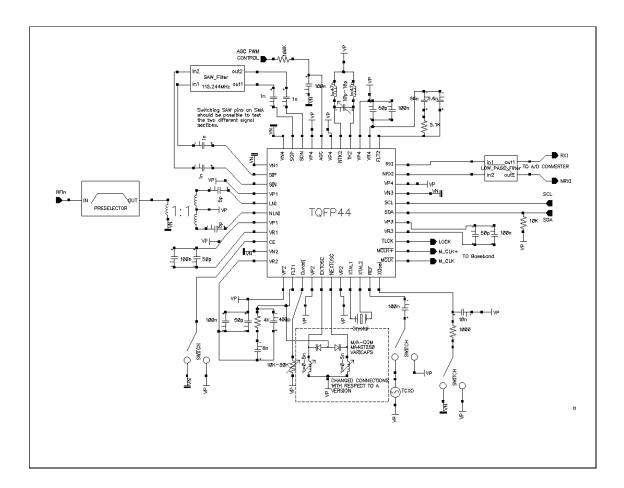

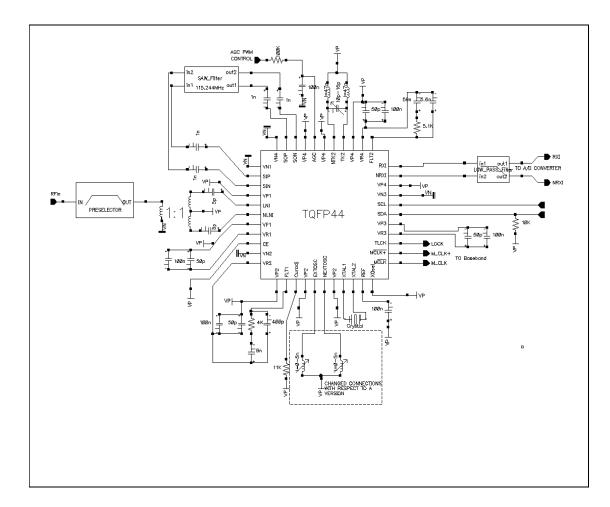

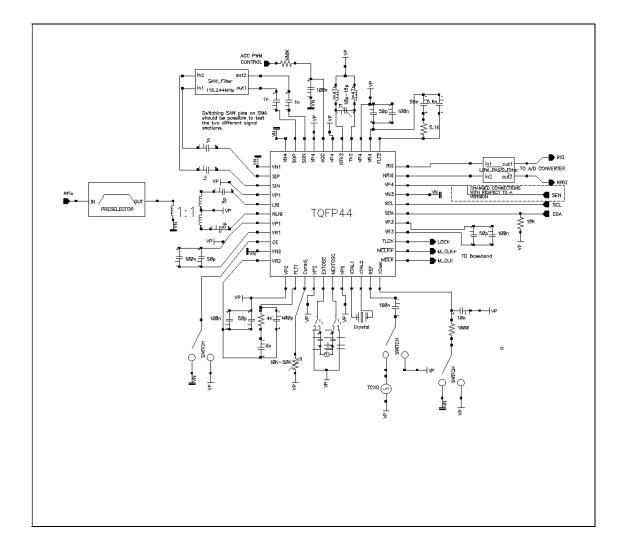

# STA001 version B Testing board

# STA001 version B Application board

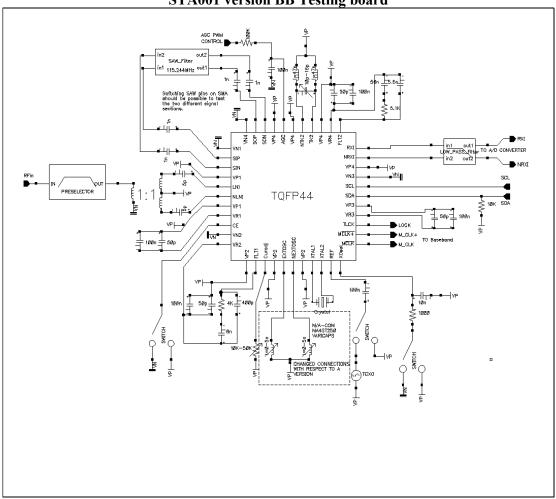

# STA001 version BB Testing board

# STA001 version BB Application board

#### STA001 version C Block diagram

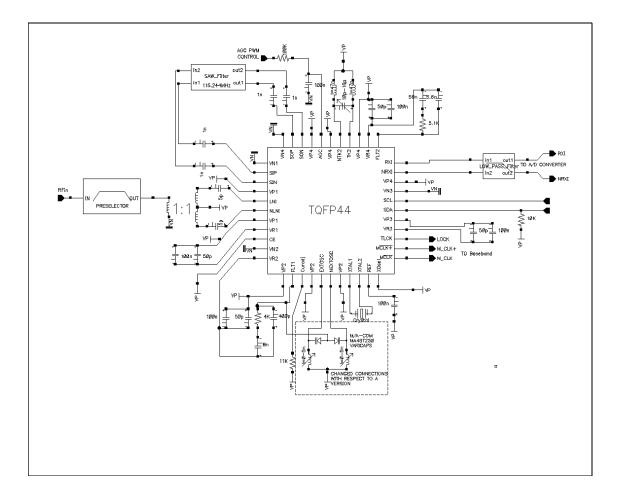

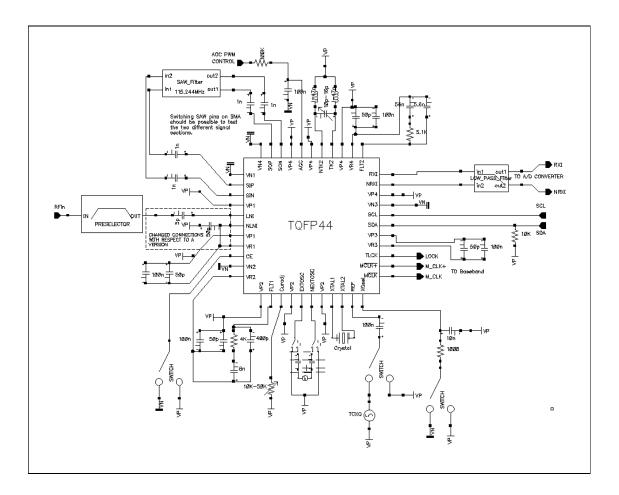

# STA001 version C Testing board

# STA001 version C Application board

#### STA001 version D Block diagram

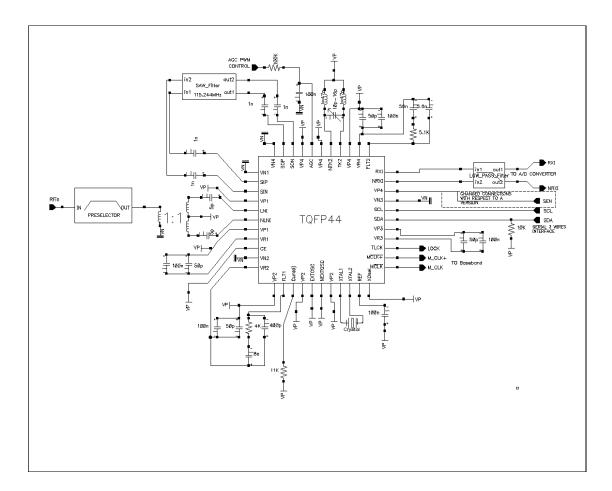

# STA001 version D Testing Board

# STA001 version D Application board

## STA001 version E Block diagram

# **STA001 version E Testing board**

# **STA001 version E Application board**