## Bibliographic data: GB976504 (A) — 1964-11-25

## Improvements in or relating to data storage arrangements

| Inventor(s):           | KILBURN TOM; EDWARDS DAVID BEVERLEY GEORGE <u>+</u><br>(KILBURN TOM, ; EDWARDS DAVID BEVERLEY GEORGE) |

|------------------------|-------------------------------------------------------------------------------------------------------|

| Applicant(s):          | NAT RES DEV $\pm$ (NATIONAL RESEARCH DEVELOPMENT CORPORATION)                                         |

| Classification:        | - international: G06F12/06; G11C11/06<br>- cooperative: G06F12/0607 (EP); G11C11/06007 (EP)           |

| Application number:    | GB19600009301 19600316                                                                                |

| Priority<br>number(s): | GB19600009301 19600316                                                                                |

| Also<br>published as:  | <u>DE1194179 (B)</u> <u>US3231361 (A)</u>                                                             |

## Abstract of GB976504 (A)

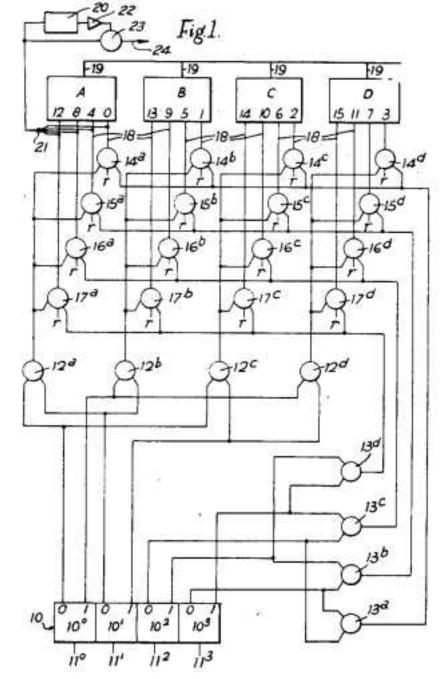

976, 504. Electric digital-data-storage. NATIONAL RESEARCH DEVELOPMENT CORPORATION. March 14, 1961 [March 16, 1960], No. 9301/60. Heading G4C. A data storage arrangement comprises a plurality of separate blocks of data word storage elements and is characterized by address selection control means arranged so that successive address numbers cause selection of word storage locations which are in different ones of said blocks. As described, a data store comprises four blocks in the form of magnetic core matrices A-D, each block storing four data words of 40 digits each. The sixteen locations in the matrices have address numbers 0, 1, 2,..., 15 in binary code, locations 0, 4, 8, 12 being in the matrix A, locations 1, 5, 9, 13 in B and so on. To address a chosen location its binarycoded address is staticised by a four-stage staticisor 10, the outputs of which are connected by an arrangement of AND gates 12a-12d, 13a-13d,..., 17a-17d to the inputs of the matrices A-D in such a way that an output is produced on that one of leads 18 corresponding to the address in the staticisor 10. Normally, locations are addressed in sequential order, but in case it is required to obtain access successively to two storage locations in the same matrix, a monostable flip-flop 20 is connected to all the leads 18 for the matrix A, the output of the flip-flop 20 being connected via a delay 22 to an AND gate 23. An output is thus provided on a lead 24 for a chosen period, which output may be arranged as an inhibiting signal to prevent the next address selection taking place in the matrix A until an appropriate recovery time for the matrix A has elapsed. A similar arrangement is provided for the matrices B, C, D. In a modification (Fig. 2, not shown), locations 0-7 are arranged

alternately in matrices A, B and locations 8-15 are arranged alternately in matrices C, D.