# The Atlas story.

# Simon Lavington.

Second edition, 6<sup>th</sup> December 2012.

# Contents.

| Introduction                                  | page | 1  |

|-----------------------------------------------|------|----|

| Birth pains                                   |      | 1  |

| Atlas at Manchester                           |      | 1  |

| Ferranti and the market place                 |      | 5  |

| Timeline                                      |      | 6  |

| Technical innovations: facts and figures      |      | 6  |

| The London Atlas                              |      | 8  |

| The Chilton Atlas                             |      | 9  |

| The Atlas 2 developments                      |      | 11 |

| Titan at Cambridge                            |      | 13 |

| Atlas 2 at AWRE Aldermaston                   |      | 13 |

| Atlas 2 at the CAD centre                     |      | 13 |

| More technical details of Atlas installations |      | 15 |

| Physical layout                               |      | 17 |

| Organisation of the Atlas storage hierarchy   |      | 17 |

| Format of an Atlas instruction.               |      | 19 |

| Guide to the Atlas Supervisor                 |      | 20 |

| People and places                             |      | 21 |

| More information                              |      | 22 |

Originally produced for the Atlas Symposium held on 5<sup>th</sup> December 2012 in the School of Computer Science, Kilburn Building, University of Manchester.

It is a pleasure to acknowledge the help given by many former Atlas pioneers in the writing of this brochure. Comments on the text are welcomed and should be sent to Simon Lavington: <a href="mailto:lavis@essex.ac.uk">lavis@essex.ac.uk</a>

Picture credits to copyright holders.

Computer Laboratory, University of Cambridge: Figure 9

Graham Penning: Figure 10

Simon Lavington: Figure 3

Iain MacCallum: Front cover

Museum of Science & Industry, Manchester Figures 1, 2, 4, 5, 6 STFC Rutherford Appleton Laboratory: Figures 7a, 7b, 8

(On 5<sup>th</sup> December the original printed version of this document had a cover design based on photographs of the Atlas at Manchester University in 1963).

By the end of 1955 there were less than 16 production digital computers in use in the UK. They were of five British designs, from five different companies, and were single-user systems with practically no systems software. They each had primary memories of 4K bytes or less and could obey about 1,000 instructions per second. Their technology was based on vacuum tubes (ie *thermionic valves*). At the end of 1955 Tom Kilburn and his research group in the Department of Electrical Engineering at the University of Manchester began to plan a much more ambitious machine. The aim was to use new technologies and new concepts to build a multi-user computer having a primary memory of at least 500K bytes and a speed of about one million instructions per second. With the help of Ferranti Ltd., these goals were more or less achieved in December 1962, when Sir John Cockcroft came to Manchester to inaugurate the first of the Ferranti Atlas supercomputers.

## Birth pains.

In 1956 two factors drove Tom Kilburn's research group: the urgent need of the UK's nuclear physicists for more powerful computers, and the knowledge that the Americans were planning new machines such as the IBM STRETCH that could probably satisfy the physicists' needs. In short, the early lead in computers that the UK had achieved in the period 1948 – 51 had slipped away. These factors were also of concern to the National Research Development Corporation (NRDC), who took it upon themselves to encourage and sponsor British companies to rise to the challenge. The first mention of the word *Supercomputer* comes in an NRDC meeting of January 1957.

NRDC took the lead in attempting to organise a British Supercomputer project on its own terms. Between 1956 and 1958 three companies and several research groups (including Manchester) were approached. Events did not go smoothly for Lord Halsbury, NRDC's Director. Writing in 1958, he said: "Were we [the UK] strong enough to compete? Ought we to try? Could we afford not to? Could any such proposal be established on a commercial basis? During the last two years I have unsuccessfully wrestled with divided counsels on all these issues." Meanwhile, Kilburn's group were pressing ahead with limited internal funds for their high-speed computer project, which was called MUSE – short for *Musec (Microsecond) Engine.* Then in 1959 Ferranti Ltd. decided to collaborate with MUSE, the joint University/Ferranti project thereupon changing its name to Atlas. NRDC had initial doubts about this venture but in the end NRDC loaned Ferranti Ltd. £300K towards the cost of Atlas development. NRDC also loaned EMI's Computer Division £250K for a high-speed computer project but this EMI project came to nothing.

#### Atlas at Manchester.

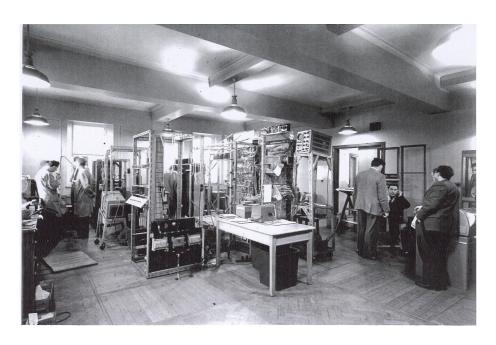

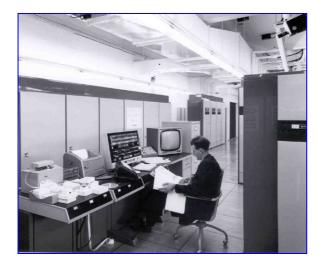

The MUSE/Atlas computer was built and installed in the University's Department of Electrical Engineering, in their new premises in Dover Street (now called the Zochonis Building, part of the Department of Psychology). Firstly, a Pilot version of Atlas was assembled and tested on the third floor in *Computing Machine Room 1*, formerly occupied by the Ferranti Mark I computer. Meanwhile the University's regular computing service was run on a Ferranti Mercury computer installed in *Computing Machine Room 2*. Figures 1 and 2 show the Pilot Atlas in the autumn of 1960, by which time the outline design of all nine Atlas sub-units had been completed and the detailed logical design of 80% of these units had been finished.

Fig. 1. The pilot Atlas in the Department of Electrical Engineering, University of Manchester, in 1960.

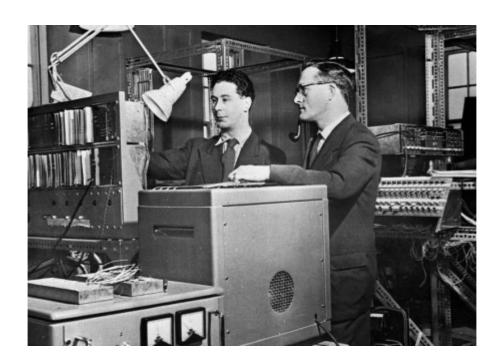

Fig. 2. Mike Lanigan (left) and Tom Kilburn (right) with the Pilot Atlas in 1960.

At this stage there were 49 types of printed-circuit board (pcb) in production or ready for production at Ferranti's West Gorton factory, plus 9 types for which the design was still incomplete. Each pcb measured about 20cm by 15 cm, as shown in Figure 3. The total number of pcbs in the final Manchester Atlas (excluding peripheral equipment) was 5,172. On the software side, the writing of high-level language compilers for Atlas was in progress by 1960, assisted by the development of a tool called the Compiler Compiler which greatly speeded the process of compiler production. At this stage, work on the Atlas Supervisor (or Operating System) was in its initial planning phase.

Fig. 3. Front and back of an Atlas type 822 printed-circuit board, containing six flip-flops. This used Mullard OC170 germanium transistors.

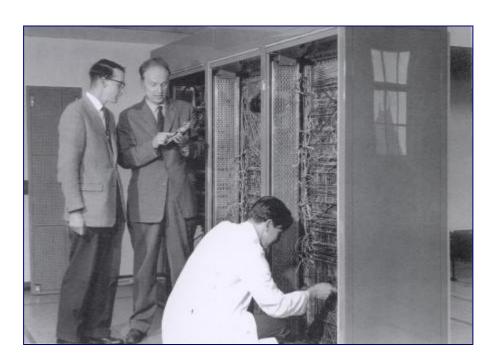

Fig. 4. The first Atlas production cabinet, containing the A and B arithmetic units, B store and the Distributor, installed in the University of Manchester in June 1961.

Alec Robinson (Ferranti) is standing to the left and Dai Edwards (University) is to the right.

The Pilot Model of Atlas was dismantled and re-assembled at West Gorton at the end of January 1961, where it was used for further development and, in due course, the training of maintenance engineers. In June the first Atlas production cabinet was delivered to

Dover Street and installed in the refurbished *Computing Machine Room 1* – see Figure 4. By this time the hardware and software design team for Atlas, led by Tom Kilburn, consisted of about 12 academics and 15 Ferranti employees – though the Ferranti contribution would double within the next 15 months. Incredible as it now seems, the Atlas Compiler group never numbered more than six full-time programmers and the Supervisor group never more than seven. For comparison, in 1957 IBM was said to be spending \$28m annually on their STRETCH supercomputer and to be deploying 300 graduates on the project.

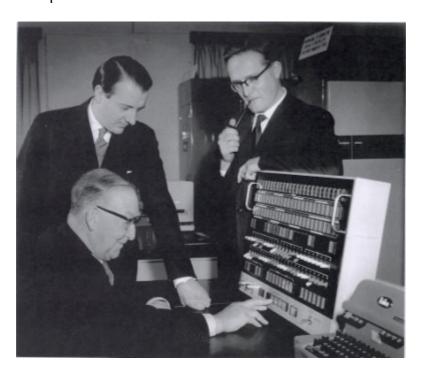

By the summer of 1962 commissioning of the Atlas hardware and the writing of the Supervisor was in full swing, with a few trusted end-users running urgent programs written in an extended form of Mercury Autocode. Although Atlas software development continued after Sir John Cockcroft's opening ceremony, a regular Computing Service was up and running by the start of 1963. However it was not until January 1964 that the final version of the Atlas Supervisor was in use.

Fig. 5. Sir John Cockcroft (seated) formally switches on Atlas at Manchester University on 7<sup>th</sup> December 1962. Sebastian de Ferranti (left) and Tom Kilburn (right) look on.

Useful time on the Manchester Atlas was shared equally between the University's Computing Service and Ferranti's Computing Service. Anything up to 1,000 user programs were being run in a 20-hour 'day'. By 1969 the annual value of computing to the University was estimated at £720,000, if costed on the open market.

In 1964 Tom Kilburn's group had split off from Electrical Engineering to form a separate Department of Computer Science. By 1969 the 'service' side of the Department's activities was formally devolved to the *University of Manchester Regional Computing Centre* (UMRCC), which the government equipped with an interim machine, an ICL 1905F, whilst a new building was being constructed.

The Manchester Atlas was closed down on 30<sup>th</sup> September 1971. The new computer building, subsequently named the *Kilburn Building*, was opened in 1972 to house the Department of Computer Science and UMRCC. By this time, Tom Kilburn's design team was involved with the implementation of a new research computer called MU5 and UMRCC had taken delivery of a CDC 7600 machine front-ended by an ICL 1906A.

UMRCC initially provided services for a group of universities which included Salford, Liverpool, Keele and Lancaster. Equipment was updated over the years and the number of universities served expanded. Then in due course each UK university began making its own provisions. The University of Manchester's current Directorate of IT Services was established in 2005 just after the merger with UMIST and still runs from the ground floor of the Kilburn Building and with IT teams across the campus.

## Ferranti and the market-place.

Costing between £2m and £3m each (equivalent to about £50m each in 2012) it was clear that UK sales of Atlas would be few in number. Ferranti therefore made strenuous efforts to market Atlas in America (principally to Atomic Energy establishments), in Australia (principally to CSIRO) and in Europe (principally to CERN). The rival IBM STRETCH computer cost more than Atlas (initially \$13.5 million, finally reduced to \$7.78 million each); only seven were delivered between 1961 and 1963. By 1964 the real threat, both to Atlas and to STRETCH, was the arrival of a new supercomputer manufacturer in America, the Control Data Corporation. The CDC 6600, which benefited from advances in silicon transistors, was about three times faster than both the IBM STRETCH and Atlas.

Only three Atlas 1 computers were delivered: to the University of Manchester, to a joint BP/London University consortium, and to the Science Research Council's laboratory at Chilton, near Harwell. The London and Chilton sites are described later.

Judging that a simpler version of Atlas might prove more commercially viable, in February 1962 Ferranti provided Cambridge University with some units of Atlas hardware on special terms, in return for help in developing a less complex machine. The result of this arrangement was the Cambridge Titan computer, the prototype for Atlas 2. This was first operational in 1964. Two other production versions of Atlas 2 were sold by Ferranti: one went to the Atomic Weapons Research Establishment at Aldermaston; the other to the Ministry of Technology's Computer-Aided Design Centre at Cambridge. The three Atlas 2 sites are described later.

Concurrent with the Atlas developments, Ferranti was also designing and implementing a large commercial data-processing computer called Orion. The Orion project was not without its difficulties. In October 1963 Ferranti's mainframe computer interests were taken over by the British company International Computers & Tabulators (ICT). By 1968 ICT had merged with all the remaining UK computer mainframe manufacturers to form International Computers Ltd. (ICL). Thus, Atlas equipment and brochures have successively carried the logos of Ferranti, ICT and finally ICL.

Commenting years later, Brian Hardisty who was a technical expert on the Atlas sales team, has said: "Not enough of the company's resources were, or indeed could responsibly have been, devoted to such a large machine as Atlas, for which there was such a relatively limited world-wide market. It would have needed enormous investment

over a long period of time to ramp up the scale of its activities, with, of course, no guarantee of a good return. So objectively it was right for Ferranti's computer department to merge with ICT, and for ICT to concentrate on more mainstream computers. But it was sad that, in all of this, Atlas eventually got sidelined".

## Timeline.

Landmarks in the Atlas world may be summarised as follows:

| 1955 | start of research at Manchester University under Tom Kilburn, leading to MUSE. |

|------|--------------------------------------------------------------------------------|

| 1959 | formal start of Ferranti/University collaborative design of Atlas.             |

| 1962 | inauguration of the first production Atlas 1 at Manchester University.         |

| 1962 | various units of Atlas hardware delivered to Cambridge                         |

| 1963 | second production Atlas 1 delivered to London                                  |

| 1964 | third production Atlas 1 delivered to Chilton.                                 |

| 1964 | Titan (aka the first Atlas 2) comes into operation at Cambridge                |

| 1964 | second production Atlas 2 delivered to AWRE Aldermaston                        |

| 1967 | third production Atlas 2 delivered to the CAD Centre                           |

| 1967 | Titan's time-sharing operating system comes into operation                     |

| 1971 | Manchester Atlas 1 closed down                                                 |

| 1971 | Alderrmaston Atlas 2 closed down                                               |

| 1972 | London Atlas 1 closed down                                                     |

| 1973 | Chilton Atlas 1 closed down                                                    |

| 1973 | Cambridge Titan (Atlas 2) closed down.                                         |

| 1976 | CAD Centre Atlas 2 closed down                                                 |

|      |                                                                                |

# Technical innovations: facts and figures.

At the outset, Tom Kilburn's team strove to achieve high performance by exploring five lines of research:

- (a) devising a fast sub-microsecond parallel adder and other logic circuits, using new transistor technology;

- (b) exploiting the latest developments in RAM and ROM memory technology so as to match access-time to the speed of the arithmetic unit;

- (c) automating the transfer of information between primary and secondary memory in an efficient manner:

- (d) automating the transfer of data from/to many relatively slow Input/Output devices and devising an efficient Interrupt system, so that delays to central computation were minimised;

- (e) providing convenient high-level programming languages and an efficient Operating System that simplified life for both operators and end-users.

In one sense the above aims could be those of a modern computer designer. In 1955 few if any of them had been attempted. Item (c) above deserves special mention. Kilburn's group defined a very large *Virtual* address space for Atlas, with hardware for translating address-references into the *Real* physical space via a set of associative (ie content-addressable) *Page-address Registers*. This *Virtual Memory* idea is seen today in all modern computers.

For item (e) above, the now-famous Compiler Compiler was developed; this greatly speeded the production of Atlas compilers for languages such as Atlas Autocode, Algol and Fortran. Speaking of the Atlas Operating System, which was called the Supervisor, Hugh Devonald who headed Ferranti's Software Division, said in 1962: 'The 'Supervisor' is the most ambitious attempt ever made to control automatically the flow of work through a computer. Its ability to handle the varied workloads that a machine of this size tackles will influence the future design of all computers.

In terms of raw instruction speed, Atlas was a little slower than its rival, the IBM STRETCH (also known as the IBM 7030). Here are some figures:

| Instruction | IBM 704<br>(1955) | Ferranti<br>Mercury<br>(1957) | IBM 7090<br>(1959) | IBM<br>STRETCH<br>(1961) | Univac<br>LARC<br>(1960) | Ferranti<br>ATLAS<br>(1962) | CDC 6600<br>(1964) |

|-------------|-------------------|-------------------------------|--------------------|--------------------------|--------------------------|-----------------------------|--------------------|

| FXPT ADD    | 24                | 60                            | 4.8                | 1.5                      | (4 ?)                    | 1.59                        | ?                  |

| FLPT ADD    | 84                | 180                           | 16.8               | 1.38 – 1.5               | 4                        | 1.61 – 2.61                 | 0.3                |

| FLPT MPY    | 204               | 300 (360)                     | 16.8 – 40.8        | 2.48 - 2.7               | 8                        | 4.97                        | 1                  |

| FLPT DIV    | 216               | ?                             | 43.2               | 9.0 - 9.9                | 28                       | 10.66 – 29.8                | 3.4                |

Instruction times in microseconds for five American and two British computers that were first installed between 1954 and 1964.

Bob Hopgood, who wrote compilers for both STRETCH and Atlas and implemented a large Quantum Chemistry package (MIDIAT) on both computers, has said:

"STRETCH could run extremely fast if you had the code set up just right and it remained in core memory. It had some terrible deficiencies as well. It made guesses as to which way a conditional jump would go and if you got it wrong it had to backup all the computation it had done. So the same conditional jump could be as much as a factor of 16 different in time between guessing right and wrong. The STRETCH nuclear weapon codes at AWRE Aldermaston probably outperformed Atlas by quite a bit. On the other hand Atlas ran some large number theory and matrix manipulation calculations much faster than STRETCH. My codes were pretty similar in performance but on large calculations where intermediate results had to be stored on magnetic tape, Atlas was significantly faster due to the Ampex tape decks. I think on an untuned general purpose workload Atlas was faster and if the code was tuned to STRETCH it would be faster. In conclusion, I would say that in 1962 'Atlas was reckoned to be the world's most powerful general-purpose computer'".

This last comment echoes Hugh Devonald, who said in 1962: "Atlas is in fact claimed to be the world's most powerful computing system. By such a claim it is meant that, if Atlas and any of its rivals were presented simultaneously with similar large sets of representative computing jobs, Atlas should complete its set ahead of all other computers."

Tom Kilburn's group at Manchester University filed 15 Atlas patents between October 1957 and February 1962, on subjects including arithmetic units, magnetic recording, storage systems and memory management. Over 20 Atlas papers were published in scientific journals between 1959 and 1968, of which a selection is given at the end. More technical details and explanatory diagrams are given below, in conjunction with descriptions of the various other Atlas installations.

Fig. 6. The London Atlas during commissioning at Ferranti's West Gorton factory in 1963.

#### The London Atlas.

In 1961 the University Grants Committee (UGC) offered to install an English Electric KDF9 computer, costing about £500,000 in London and in four other UK universities. London judged a KDF9 to be inadequate for the needs of all the colleges, so arrangements were made to put the UGC's £500,000 towards a much more powerful computer. The purchase of a Ferranti Atlas 1, at a cost of about £2 million, became the fund-raising target. British Petroleum (BP) was identified as an Atlas partner. BP agreed to put £500,000 towards purchase of a London Atlas, in return for up to one 8-hour shift of Atlas machine-time every day for five years. The University borrowed the remaining £1million, the loan to be repaid by selling Atlas machine time and by running applications for commercial clients. A Bureau called the *University of London Atlas Computing Service* (ULACS, or simply ACS) was set up for this purpose. On the open market, an hour of Atlas machine-time was worth about £750.

Alec Robinson was the ULACS Manager. A specially-constructed two-storey building adjacent to Gordon Square, Bloomsbury, was completed in 1963. As with the Chilton installation (see below), peripheral equipment was on the upper floor and the Atlas mainframe on the lower floor. Delivery of the London Atlas commenced in October 1963. A technical description of the configuration is given later.

In about 1962 the *University of London Institute of Computer Science (ICS)* under Professor R A Buckingham was set up to support and provide academic research, postgraduate teaching, computer services and network services. In practice, the Institute was closely associated with the Atlas Computing Service (ACS). Both ICS and ACS were co-located in Gordon Square, Bloomsbury.

ACS was responsible for a significant amount of Atlas software development during the period 1964 to 1972, often in collaboration with the Institute of Computer Science (ICS). Amongst the software originating from ACS and ICS was:

Fortran V, a superset of the then-available Fortran IV;

Atlas Commercial Language (ACL);

MVC (Multi-Variate Counter), a survey-analysis system;

BCL, a machine-independent type of Compiler-Compiler;

*CPL*, an implementation of the original language developed by a combined team from Cambridge and ICS. CPL was intended as a powerful Algol-like language that catered for an extremely wide variety of applications – ranging from low-level programming for industrial process-control to commercial business data processing. A preliminary version of CPL was introduced at London in 1966.

In terms of computing resource, the benefit of Atlas to London University was reduced over the years, as more and more of the London colleges acquired their own computers. A new *University of London Computer Centre (ULCC)* was created in 1968, following the recommendation of the Flowers Report on the establishment of Regional Computing Centres at Edinburgh, London and Manchester. A CDC 6600 computer, rated at about three times the power of Atlas, was installed in ULCC in June 1969. The London Atlas was finally switched off on 30<sup>th</sup> September 1972.

#### The Chilton Atlas.

This Atlas site has variously been referred to as NIRNS, Harwell, Chilton or RAL, so a word of explanation is helpful. The National Institute for Research in Nuclear Science (NIRNS) was formed in 1957 to operate the Rutherford High Energy Laboratory as an open-access nuclear research facility, located just outside the perimeter fence of the United Kingdom Atomic Energy Authority's (UKAEA's) restricted-access laboratory at Harwell. NIRNS itself lay between the villages of Chilton and Harwell, so 'Chilton' became the informal name for NIRNS. The umbrella organisation for the Chilton Atlas was the UK's Science Research Council (SRC), whose central computing facilities have, since 2007, been run by the Science and Technology Facilities Council (STFC).

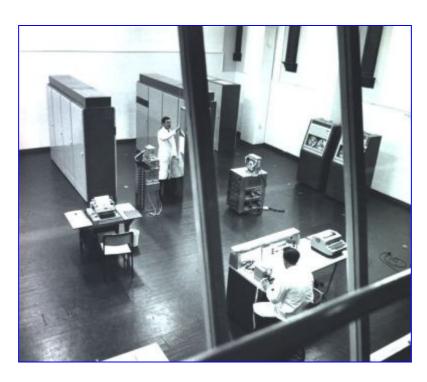

Fig. 7. These two views of an engineer sitting at the console of the Chilton Atlas give an idea of the size of the machine room. Input/output equipment was in the room directly above – (see Fig. 8).

The Chilton Atlas had been ordered from Ferranti in the summer of 1961. A specially-designed building, the *Atlas Computer Laboratory,* was ready in 1964 and the machine was installed in May and June of that year. It was the largest of the three Atlas 1s, as can be seen from the technical specifications given later.

Fig. 8. The input/output area for the Chilton Atlas. The person just to the left of the lineprinter in the centre of the picture is David Howarth.

By 1966 the Atlas Computer Laboratory was processing an impressive number of programs each day. The Director, Jack Howlett, was able to write in his annual Report: "In a typical week we run 2,500 jobs, input 800,000 cards and 30 miles of paper tape, print 1.8 million lines of output, punch 50,000 cards, handle 1,200 reels of magnetic tape. We have 250 projects on our books from university users and are usually doing work on 100 of these.... Our experience over the past year has shown that the Atlas central processor, with the Supervisor which is an integral part of the system, is an exceedingly powerful and flexible device which deals smoothly and efficiently with a heavy load of very varied work".

However, by 1966 programmers' expectations were gradually changing. Encouraged by experiments in multi-access timesharing facilities being conducted in America, the emphasis was moving away from efficient use of mainframe hardware and towards efficient use of programmer's time. From 1966 to 1970 the Chilton Atlas was enhanced by provision of better file-manipulation facilities, together with time-sharing via a number of interactive terminals. This required investment in two major pieces of hardware: a large 16m word disk store and a Sigma 2 satellite computer. In due course the Chilton Atlas was able to support 32 online terminals (Cossor VDUs), up to eight of which could be active at any one time.

Over the years a number of specialist peripherals were also attached to the Chilton Atlas. Amongst these was a Stromberg Carlson SC4020 Microfilm Recorder, a D-MAC graphical

input table, an Opscan Optical Character Recognition device and an Optronics Microdensitometer. Interactive graphics was introduced in 1970 by connecting a PDP15 computer with a VT15 display to Atlas.

Over the life of the Chilton Atlas approximately 85% of available computing time had been devoted to UK universities, during which 2,300 research projects had been supported. The remaining 15% of computing time was used by government departments for applications such as weather forecasting and space research. Over the years, the Chilton staff found that there were certain areas where the needs of most users could be met by general programs, which staff then provided - either writing them or acquiring (and adapting) them from other sources. Amongst such areas were:

Crystallography, particularly the interpretation of x-ray diffraction patterns; Computational Chemistry: calculating the structures and properties of molecules; Finite-element analysis: Mostly for engineering structures.

Time-series analysis: Used to detect patterns or variations in recorded phenomena; Text analysis: Investigation of quantitative features of natural-language texts; Survey analysis: Applications included the study of medical or social questions.

The Chilton Atlas was closed down on 30<sup>th</sup> March 1973 and the main hardware units were presented to the National Museums Scotland, where they remain to this day in storage.

# The Atlas 2 developments.

In 1961 the University of Cambridge, finding itself in a somewhat similar situation to London, needed a new computer that was more powerful than could be purchased with the limited funds available at that time. Peter Hall, Ferranti's Computer Manager, suggested that Ferranti sell Cambridge the main processing units of Atlas at 'works cost', for which Cambridge and Ferranti would then jointly design and implement a simpler memory system and simpler arrangements for peripheral equipment. The result would be a computer for Cambridge which would also be the prototype of a cheaper version of Atlas for Ferranti to market. The machine was officially named Titan, in line with the Ferranti tradition of choosing names from classical mythology, but was later re-named Atlas 2 by the marketing people. In Cambridge the name Titan stuck as the prototype of Atlas 2.

# Titan at Cambridge.

Atlas hardware arrived in Cambridge in 1963, by which time the software design had already started on paper. David Wheeler was design authority for the joint Cambridge/Ferranti team responsible for specifying the new sections of hardware. Titan's memory-management system was initially based on 32K words of core memory (no drums) with a single base and limit pair of registers and two other registers to lock peripheral transfers. This clearly gave a huge saving in hardware costs compared with the original Atlas paging hardware and one-level store concept. Nevertheless, Titan's memory control allowed full user protection so that, even though multiple programs might be active, a program could only read from or write to the area specified in the control registers. The major drawback was that the storage allocated to one program had to be contiguous in real memory. Titan's core store was later increased to 64K, and finally to 128K words, all with a cycle-time of 5 microseconds.

Fig. 9. The Cambridge Titan computer, prototype of the Atlas 2, photographed from the viewing gallery.

In addition to the above new hardware, Titan was equipped with two experimental caches, based on tunnel diodes. One of these, called the *Fast Operand Store*, buffered the contents of users' addresses 0-7 and worked well. The second, called the *Slave Store*, was a 32-line instruction buffer intended for loops of 32 or less instructions. The *Slave Store* proved unreliable. Titan had no fixed store, so Extracode routines were implemented entirely in main memory.

On the software side, a joint Ferranti/Cambridge team worked on the Atlas 2 Supervisor. This was a multiprogramming job-shop Operating System, similar in scope to the Supervisor of the larger Atlas 1 machines. In due course the team divided into two: the Cambridge contingent intended to finish the system as planned, whilst the Ferranti people modified the system to suit Aldermaston (see below).

However in 1965 the Cambridge team decided to change direction in order to provide Time Sharing facilities for Titan via interactive terminals. To achieve this, more hardware was needed. Firstly, an additional pair of memory location registers (enabling a shared program controlled by the first pair to have a dedicated piece of data controlled by the second pair) were provided, together with a further base pointer to a single piece of 64-word store. Secondly, a large file disk, the gift of Basil de Ferranti, was attached. Finally, a terminal multiplexor was designed and built to enable 64 devices to connect to the system. Eventually a second file disk was added.

Thus when the Cambridge Atlas 2 (aka Titan) finally came into full service in 1966, time sharing facilities were available for staff. By March 1967 time-sharing had been extended to other users and interactive graphics techniques via an attached PDP7 computer were being pioneered. Titan was finally switched off in October 1973.

#### Atlas 2 at AWRE Aldermaston.

The Atomic Weapons Research Establishment (AWRE) at Aldermaston hired an IBM STRETCH computer in the summer of 1962. Then in November 1963 AWRE decided to buy an Atlas 2 to operate alongside the IBM machine. An Atlas 2 was delivered at the end of 1964. Put simply, Atlas 2 had a somewhat similar arithmetical speed as Atlas 1 but without the flexibility and power of the one-level store. It was therefore much cheaper. In Aldermaston's case, AWRE were not prepared to accept multi-programming (ie more than one user-program in memory at a time) on security grounds. Aldermaston's Supervisor was thus a restricted version of the original pre-1965 Titan Supervisor.

Aldermaston's Atlas 2 had 128K words (48 bits) of core memory, eight Potter one-inch magnetic tape decks, and two IBM half-inch tape decks for data-interchange purposes. There were the usual punched paper tape and punched card input/output devices. The full complement of peripheral equipment was installed over several months but, once complete, the configuration is believed to have remained static throughout the operational life of the computer.

AWRE depended critically on the run-time quality of Fortran. The IBM STRETCH's Fortran compiler was judged not fit for purpose. Alick Glennie, who was in charge of software development at AWRE, wrote the first of three Fortran compilers for STRETCH in late 1962. From 1965 onwards Atlas 2 and STRETCH were operated alongside each other at AWRE, running the same Fortran user system S3 (which was itself embedded in the Atlas 1 Hartran system). Glennie's S3 compiler had full subroutine optimisation and innovative loop unwinding and was judged to be one of the best Fortran compilers around at the time. It is believed that Atlas 2 at Aldermaston was switched off in 1971 at about the same time as the STRETCH system was removed, to be replaced by an IBM 360/75.

# Atlas 2 at the CAD Centre.

In July 1966 Tony Benn became the new Minister of Technology. He was keen for the government to assist industry in adopting new technology and was also keen to support British computer manufacturers. These two desires came together when the government agreed to purchase from ICT the third and final Atlas 2 computer (which had proved difficult to sell) and use it to establish a Ministry of Technology Computer-Aided Design Centre at Madingley Road, Cambridge.

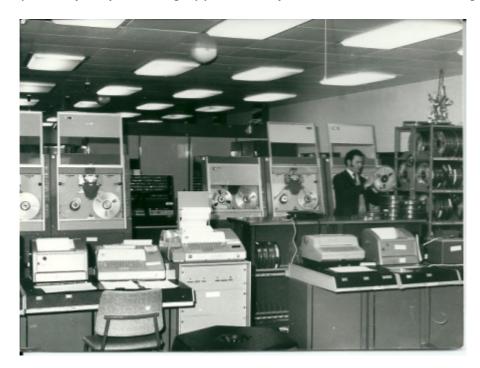

In the late summer of 1967, installation of the MinTech CAD Atlas 2 commenced. The machine had 256K words (48-bits each) of main core store, a 27 million word disk, six one-inch magnetic tape decks and the usual lineprinters and paper tape input/output and card input equipment. The CAD Atlas 2 ran the Titan timesharing operating system developed at Cambridge University. Indeed, the CAD Centre Atlas 2 ran the University's Computing Service 'transparently' for a short time while Titan was being moved from one building to another in 1969.

The first Director of the CAD Centre was Arthur Llewellyn. The computer operating staff was provided by ICT/ICL under contract from the Ministry of Technology. The CAD Centre personnel were structured into two main groups: *Computers and Networks* and *Applications*. The applications areas included Mechanical Engineering, Civil Engineering and Electronics. By 1969 there were about 100 scientists and engineers at the CAD

Centre. There was no expectation that the organisation would ever be profitable, with contract work probably only covering approximately 10% of the annual running costs.

Fig. 10. The Atlas 2 at the Computer-Aided Design Centre.

Specialist equipment was connected to Atlas 2 for visualisation and graphical input/output, along with conventional ASR33 teletypes for general on-line program development. Over the years, the CAD Centre acquired a number of smaller satellite computers, some of which were connected to Atlas 2. An early acquisition was a Digital Equipment PDP-9 computer, attached to which was a large circular display and light pen. Besides the PDP-9, the following computers were eventually acquired by the CAD Centre:

Elliott 905 computer with a model 928 display with light pen; CTL Modular One computer, with a half-inch magnetic tape system; DEC PDP-11.

Amongst the client organisations using Atlas were the following:

- Pye Telecommunications Ltd., a thriving Cambridge electronics company;

- De La Rue, who designed the complicated mathematical patterns for banknotes;

- Ricardo, an engineering consultancy, who used the CAD Centre for thermodynamic calculations for car engines;

- the Transport and Road Research Laboratory (TRRL)) designing road signs and producing 3-D visualisations of approaches to junctions/roundabouts etc.

- Applied Research of Cambridge (ARC), doing work on modular hospital design.

- Whessoe doing pipework design for chemical plants (PDMS).

- The Admiralty Underwater Weapons Establishment;

- GCHQ.

In 1972 the CAD Centre's Systems Group started to design and implement a pioneering UK network that would enable users to access remotely the multitude of powerful design packages that were becoming available on other computers at other sites. By 1974 the

CAD Centre at Cambridge had links with the following four other sites, via the Star Network:

National Engineering Laboratory, East Kilbride, Scotland; (UNIVAC 1108) SCICON Computer Services Ltd., Milton Keynes; (UNIVAC 1108)

SIA Ltd., Lower Belgrave Street, London; (CDC 6600 and CDC Cyber 72) CAD Centre, St Helens, Lancashire; (ICL 1904A).

The Star Network gave users a wide range of specialist graphical input/output equipment and access to the latest applications software. This software comprised over 300 design packages, of which many had originating from the Cambridge CAD Centre.

On 21st December 1976 the Atlas 2 at the CAD Centre was switched off for the last time. By now, the emphasis was turning to the cluster of front-end and satellite computers at Madingley Road, chief amongst which was a Prime 300 computer. The CAD Centre was privatised by the Thatcher Government in 1983 as CAD Centre Ltd. It became a publiclyquoted company in 1996 and changed its name to AVEVA plc in 2001. At the time of writing, AVEVA is thriving. The CAD Centre, together with the Cambridge Science Park (founded in 1970), were the two important contributors to the growth of the town of Cambridge as a major centre for advanced technology and innovation – the region sometimes being known as Silicon Fen.

### More technical details of Atlas installations.

The three larger Atlas 1 installations differed mainly in the amount of core store (RAM) and the number of magnetic tape decks. Here is the state of play in November 1966:

|                                 | Manchester       | London Atlas      | Chilton Atlas     |

|---------------------------------|------------------|-------------------|-------------------|

|                                 | Atlas            |                   |                   |

| Core store (48-bit words)       | 16K              | 32K               | 48K               |

| (cycle-time = 2 microseconds)   | (in two pairs of | (in four pairs of | (in six pairs of  |

|                                 | stacks, 4-way    | stacks, 4-way     | stacks, 4-way     |

|                                 | interleaved)     | interleaved)      | interleaved)      |

| Ampex TM2 one-inch              | 8 decks          | 14 decks          | 16 decks          |

| magnetic tape decks             | (8 channels)     | (8 channels with  | (8 channels with  |

| (transfer-rate = 90K characters |                  | four 2x8          | one 2x8 switching |

| per second).                    |                  | switching         | unit)             |

| ,                               |                  | units)            |                   |

| IBM-compatible half-inch        | -                | 2 Potter type     | 2 IBM type        |

| magnetic tape decks             |                  | MT-120 decks      | 729 decks         |

Each of the above computers also had the following units of storage:

B store (eg index registers): 128 half-words (24 bits), cycle-time = 0.7 microseconds.

Fixed store (ROM): 8K words, access-time = 0.3 microseconds. Supervisor Working Store: 1K words, cycle-time = 2 microseconds.

4 drums, each 24K words. Drum store:

(rev. time = 12.67 milliseconds; transfer-time = 2 milliseconds

per block of 512 words).

In addition, a large file disk (a Data Products model 5045, of capacity 16.8 million 48-bit words with two independent read-write mechanisms) was added to the Manchester Atlas (in October 1967) and to the Chilton Atlas (in February 1968).

The three Atlas 1 computers also had slight differences in their conventional input/output equipment, reflecting not only local work-patterns but also estimated user-preferences for punched paper tape or punched cards. Here is the state in November 1966. The right-hand column in the Table shows the maximum number of devices of each type that can be accommodated by the Atlas 1 Peripheral Coordinator.

|                                            | Manchester | London | Chilton | Max number permitted |

|--------------------------------------------|------------|--------|---------|----------------------|

| Fast paper-tape readers (1,000 chars/sec.) | 1          | -      | 1       | 4                    |

| Slow paper tape readers (300 chars/sec.)   | 4          | 5      | 3       | 8                    |

| Fast paper tape punches (300 chars/sec.):  | 1          | -      | ı       | 4                    |

| Slow paper tape punches (110 chars/sec.):  | 4          | 3      | 3       | 8                    |

| Card readers (600 cards/min.):             | 1          | 2      | 2       | 4                    |

| Card punches (100 cards/min.):             | 1          | 1      | 2       | 2                    |

| Lineprinters (1,000 lines/min.):           | 2          | 2      | 2       | 4                    |

| Slow teleprinters (10 chars/sec.)          | 2          | 4      | 3       | 4                    |

In due course, each of the above sites established a limited number of dedicated connections (*Datalinks*) via rented telephone lines to other organisations. When compared with today's Internet, these connections were primitive and slow; at the time they were very cost-effective. By November 1966 the Manchester Atlas had two ICT 7000 on-line datalink terminals and one Ferranti high-speed terminal. The London Atlas had two ICT 7000 on-line datalink terminals and one AT&E terminal. The Manchester and Chilton sites also each had a few special input/output devices attached. The Chilton devices have been listed earlier. The Manchester site had an on-line X-ray Diffractometer and an on-line A/D/A Converter (called the *Speech Converter*).

The three smaller Atlas 2 installations mainly differed in the size and cycle-time of the main core store, the presence or absence of a file disk, the nature of the Supervisor and the number of Potter one-inch magnetic tape decks. This is believed to have been the final configuration of each machine:

|                                    | Cambridge Titan                |       | CAD Centre Atlas 2 |  |

|------------------------------------|--------------------------------|-------|--------------------|--|

| Main core store                    | 128K;                          | 128K; | 256K;              |  |

| size (48-bit words) and cycle-time |                                |       | ?? microsecs       |  |

| File disk?                         | ile disk? Two, each 16m words  |       | One, 27m words     |  |

| Operating system                   | ting system Titan multi-access |       | Titan multi-access |  |

| Number of tape decks 6?            |                                | 8     | 6                  |  |

### Physical layout.

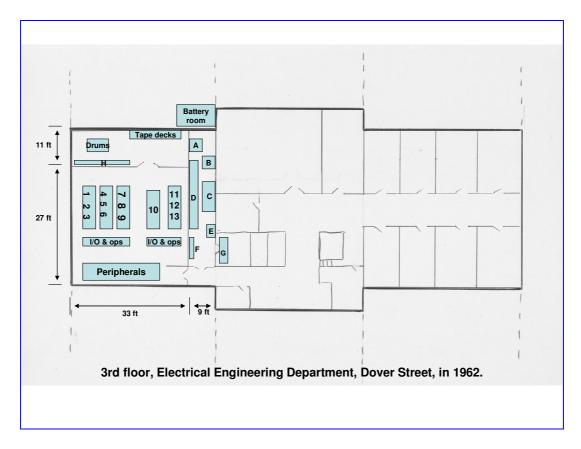

The layout (floor plan) of each Atlas site differed, with the largest installation (the Chilton Atlas) occupying a total area of 12,100 sq. ft. on two floors. In today's age of the silicon chip, it is easy to forget what was meant by 'large' in 1962 so the Manchester installation will be used as an example.

Fig. 11. The initial floor plan of the Manchester Atlas. See text for key to annotations.

The Manchester Atlas occupied the most cramped Atlas site (approx. 1,220 sq. ft.). Figure 11 shows the initial floor plan of the third floor of the Department of Electrical Engineering in Dover Street, with Atlas installed in *Computing Machine Room 1* – (a Ferranti Mercury computer was located in the adjacent *Computing Machine Room 2* until Mercury's removal in 1963). The key to the units in Figure 11 is as follows:

- A Refrigeration unit

- B Plessey core store PSU

- C Motor/alternator set

- D Lancashire Dynamo Ltd. PSU & refrigeration (later moved to plant room on the roof)

- E Mercury cubicle (for DC power supply switching)

- F Fuse panel

- G Motor/alternator set (later moved to the basement)

- H Distribution panel, feeding power to the main Atlas computer cabinets.

Bays in the five main Atlas computer cabinets (see also Figure 12 below):

- 1 Plessey core store (stacks 2 & 3)

- 2 Core store coordinator & PARs

- 3 Plessey core store (stacks 0 & 1)

- 4 1K Working store

- 5 Drum coordinator

- 6 Peripheral coordinator

- 7 Distributor

- 8 Control, B store, B-arith unit

- 9 Floating-point arith unit

11 − 13 Tape coordinator & buffer store.

# Organisation of the Atlas storage hierarchy.

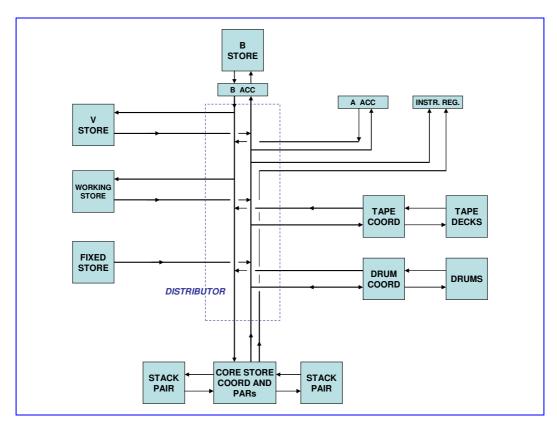

Fig. 12. information flow in Atlas.

Figure 12 shows the information flow within the Atlas central processor. The majority of the data-highways are 50 bits wide – (48 data bits plus two parity bits). In Figure 12 there are three units of system storage, access to which is forbidden by user-programs. Firstly, the *V Store* is the collective name of all the control and data registers scattered throughout the CPU and the peripherals; these are concerned with exception-handling, data transfer and interrupt-handling – (there are about 150 distinguishable causes for interruption, grouped according to priority). Secondly, the *Working Store* is used by the Supervisor for subsidiary storage. Thirdly, the *Fixed Store* contains *Extracodes*, certain library functions, and the Supervisor code and parameters for such tasks as exception-handling, peripheral transfers, and memory management.

Referring again to Figure 12, the stacks of core store (RAM) and the drum stores together form a *One-level Store*, the management of which is assisted by *virtual-to-real* address-translation via a set of *page-address registers* (*PARs*). Transfers between drums and magnetic tapes and the core store are autonomous, under the control of priority circuits.

The majority of the 128 locations in the *B Store* in Figure 12 are generally available for use as modifiers, counters, etc. However some locations are reserved for special actions, amongst which are:

B123: gives the identity of the highest-priority Interrupt currently requiring attention.

B125: the Program Counter for Interrupt Control

B126: the Program Counter for Extracode Control

B127: the Program Counter for Main Control.

Atlas has two parallel arithmetic/logic units: A and B. Each has an accumulator register, as shown diagrammatically in Figure 12. The two arithmetic units can operate in an overlapped manner and indeed several instructions may be in part-execution at any one time. Atlas is an asynchronous computer – ie there is no CPU 'clock'.

#### Format of an Atlas instruction.

The layout of an Atlas 48-bit instruction is:

| Function | Ва     | Bm     | Address |

|----------|--------|--------|---------|

| 10 bits  | 7 bits | 7 bits | 24 bits |

The interpretation of the most-significant three address-bits determines which unit of storage is referred to, as follows:

0xx the main One-level Store, available to user-programs

100 the Fixed Store

110 the V Store.

111 the Working Store

20 address-bits give the location of a 48-bit word; a full 24-bit address gives access down to the level of a 6-bit character. The Atlas Supervisor maintains a directory of all 512-word blocks of information within the machine, identified by program number and block number. An individual programmer may refer to any word, regardless of the addresses used by other programs and regardless of the physical size of the store. The only restriction is that the total number of different blocks referred to by all the programs in the machine at any one time cannot exceed the number of blocks actually existing.

The *Function* field defines the Op Code. If the most-significant digit of this field is set, then an Extracode is indicated and a library routine in the Atlas Fixed Store is automatically executed. If the ms digit is not set, then the instruction is executed directly, either by the A-arithmetic unit or the B-arithmetic unit as appropriate. There are about 250 extracodes. Besides the usual trigonometric and logarithm functions, extracodes are provided for such things as the summation of polynomials and the integration of differential equations.

The time taken by an individual instruction varies according to the number of address-modifications called for (0, 1 or 2), whether the instruction itself is in fixed store or core store, and whether the operand is in fixed store or core store. A single floating-point add instruction may take between 1.2 and 2.61 microseconds.

### Guide to the Atlas Supervisor.

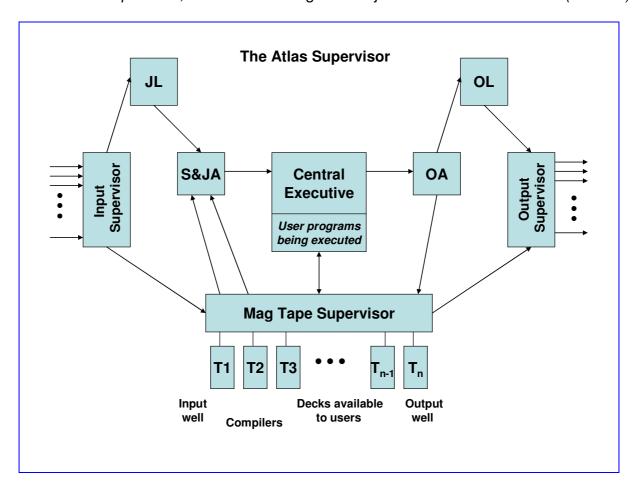

User programs are executed in a multiprogramming environment, meaning that several user-programs may be in part-execution at any one time. The task of the Supervisor is to

handle the computer's workload in a safe and efficient manner. Figure 13 shows in a simplified manner the main functions of the Supervisor. On the left of the diagram, many input devices each feed jobs (ie programs and their data) into the *Input Supervisor*. A job may consist of up to 16 documents. The *Input Supervisor* puts jobs onto a magnetic tape reserved as an *Input Well*, whilst maintaining a list of jobs in the box labelled **JL** (*Job List*).

Fig. 13. Basic functional sections of the Atlas Supervisor.

The box labelled **S&JA** in Figure 13 is the *Scheduler and Job Assembly* whose task, in simplified terms, is twofold. Firstly, all the documents associated with each user-program are assembled into complete *jobs*. Secondly, two queues are formed of jobs waiting to run. One queue is for jobs *not* requiring private magnetic tapes; the other queue is for jobs that *do* require their own reel(s) of magnetic tape. A secondary criterion in forming the queues is to try and balance the load on peripheral equipment.

The *Central Executive* organises: (a) program-switching; (b) memory-management of the One-Level Store; (c) error-monitoring, checking and recovery; (d) the action of extracodes.

The box labelled **OA** (Output Assembly) puts completed work onto a magnetic tape reserved as an Output Well, whilst maintaining a list (in box **OL**) of documents waiting to be output. On the right of Figure 13, the Output Supervisor feeds documents (eg results and monitoring information) to each of potentially many output devices. Input/output from any special equipment, such as the on-line X-ray Diffractometer at Manchester, would go directly into and out of the box labelled Central Executive.

The Atlas supervisor consisted of some 35,000 machine instructions.

# People and places.

It is impossible to mention all the hundreds of people – researchers, implementers, managers – who contributed to the hardware and software of Atlas 1 and Atlas 2. Here are just a few names, listed alphabetically at the place where they were probably most active. (Many of the Ferranti employees worked on more than one installation).

# Manchester University/Ferranti West Gorton/Ferranti Newman Street.

David Aspinall, Don Atkinson, Keith Bowden, Tony Brooker, Yao Chen, Reg Claber, John Clegg, Ben Cooper, Jim Doughty, Peter Duncanson, Eric Dunstan, Dai Edwards, Dick Grimsdale, Gordon Haley, Peter Hall, Brian Hardisty, David Howarth, Keith Howker, Peter Jones, Robin Kerr, Tom Kilburn, Peter King, Ron Lane, Mike Lanigan, Keith Lonsdale, lain MacCallum, Frank McAulay, Derrick Morris, Peter Mumford, Brian Napper, Phil Patience, Bruce Payne, Paddy Podesta, Jeff Rohl, Dave Smith, Frank Sumner, Eric Sunderland, Gareth Thomas, Ianto Warburton, Peter Warn, Pete Whitehead, Mike Wyld.

# London University: Atlas Computing Service

Mike Bernal, Dick Buckingham, John Buxton, Andrew Colin, George Coulouris, John Crowther, David Hendry, Eric Nixon, Peter Parker, Alec Robinson.

# Chilton: Atlas Computer Laboratory

John Baldwin, Mike Bayliss, Alex Bell, Paul Bryant, Bob Churchhouse, Bart Fossey, Jim Hailstone, Bob Hopgood, Jack Howlett, Doug House, Paul Nelson, Ian Pyle, Barbara Stokoe, Eric Thomas.

### Cambridge Mathematical Laboratory/Ferranti Lily Hill (Titan & Atlas 2)

David Barron, David Barton, Steve Bourne, Philip Brenan, Brian Chapman, Mike Dodd, Sandy Fraser, Mike Guy, David Hartley, Richard Jennings, Barry Landy, Charles Lang, Johnny Moore, Roger Needham, Bernard Pearson, Peter Radford, Martin Richards, Chris Spooner, Christopher Strachey, Peter Swinnerton-Dyer, Tom Wansbrough, David Wheeler, Maurice Wilkes, Neil Wiseman, Mike Vickers, John Viner,

#### AWRE Aldermaston

Alick Glennie, Florence Rigg, Mary Thomas

### CAD Centre, Cambridge, during the Atlas 2 period.

Brian Gott, John Chilvers, Alan Clarke, Chris Fell, Arthur Llewelyn, Dick Newell, Martin Newell, Graham Penning, Tom Sancha.

#### More information.

For a general picture of what it was like to install, use and upgrade an Atlas computer, see: <a href="http://www.chilton-computing.org.uk/acl/technology/atlas/overview.htm">http://www.chilton-computing.org.uk/acl/technology/atlas/overview.htm</a> An idea of Ferranti's involvement in computer design and manufacture from 1949 to 1963 can be found at: <a href="https://www.ourcomputerheritage.org/">www.ourcomputerheritage.org/</a> Many interesting Atlas manuals and original documents are held in the Ferranti Archive at the Museum of Science & Industry, Manchester: <a href="https://www.mosi.org.uk/">www.mosi.org.uk/</a> Finally, a number of specialist Anniversary documents have been prepared and are available on our website: <a href="https://www.cs.manchester.ac.uk/Atlas50/">www.cs.manchester.ac.uk/Atlas50/</a> Amongst these documents are:

- (1). NRDC and the case for a British supercomputer, 1956 1960.

- (2). Timeline of the MUSE/Atlas project at Manchester University, 1955 1971.

- (3). The Compiler Compiler Reflections of a User 50 Years On.

- (4). Memories of Atlas Fortran.

We encourage feedback and discussion, via the Atlas blog.

For the technically-minded, here is a small selection from the many contemporary articles that describe Atlas hardware and software.

#### The overall Atlas systems architecture and Virtual Memory\*:

(a). Kilburn, T, Edwards, D B G, Lanigan, M J and Sumner, F H, *One level storage system*. IRE Trans on Electronic Computers, Vol. EC-11, No. 2, April 1962, pages 223 – 235.

(b). Sumner, F H, Haley, G and Chen, E C Y, *The central control unit of the Atlas computer*. Proc. IFIP Congress, 1962, pages 657 – 663.

#### The Atlas fixed store (ROM).

Kilburn, T and Grimsdale, R L, *A digital computer store with very short read time.* Proc. IEE, Vol. 107, Part B, No. 36, Nov. 1960, pages 567 – 572.

#### Atlas arithmetic unit details:

Kilburn, T, Edwards, D B G and Aspinall, D, *A parallel arithmetic unit using a saturated transistor fast-carry circuit.* Proc. IEE, Vol. 107, Part B, No. 36, Nov. 1960, pages 573 – 584.

#### Atlas Supervisor details:

(a). Kilburn, T, Howarth, D J, Payne, R B and Sumner, F H, *The Manchester University Atlas operating system: Part 1, internal organisation.* Computer Journal, Vol. 4, No. 3, 1961, pages 222 – 225. *Part 2, users description.* Computer Journal, Vol. 4, No. 3, 1961, pages 226 – 229.

(b). Howarth, D J, Jones, P D and Wyld, M T, *The Atlas Scheduling System.* Computer Journal, Vol. 5 No. 3, November 1962, pages 238 – 244.

### Atlas Compilers and languages

(a). Brooker R A, MacCallum I R, Morris D and Rohl J S, *The Compiler Compiler*. Annual Review of Automatic Programming Vol 3, 1963, page 229. Published by London Pergamon, London." (b). Morris, D and Rohl, J S, *The Atlas compiler system*. Computer Journal, Vol. 10, 1967, pages 227 – 230.

(c). Brooker, R A, Rohl, J S and Clark, S R, *The main features of the Atlas Autocode*. Computer Journal, Vol. 8, 1965, pages 303 – 310.

#### Titan/Atlas 2 timesharing operating system

Hartley, D. F., and Needham, R. M. *Operation experience with the Cambridge multiaccess system*. IEE Conference Publication No. 55, 255-260, 1969.

#### Chilton Atlas timesharing operating system

J Baldwin and E Thomas, *Multi-access on the Chilton Atlas.* Computer Journal vol. 14, issue 2, 1971, pages 119 – 122.

\* "The Atlas project produced the patents for **Virtual Memory**. I would claim that Virtual Memory is the most significant computer design development in the last 50 years. Certainly it is the most widely used". Robin Kerr, a member of the Atlas team at Manchester from 1959 to 1964. Robin subsequently worked for a number of American computing corporations, including Control Data, GE's Corporate Research Labs and Schlumberger.